## TRANSPONDER BASE STATION IC

Check for Samples: TMS3705

#### **FEATURES**

- Base Station IC for TI-RFid<sup>™</sup> RF Identification Systems

- Drives Antenna

- Sends Modulated Data to Antenna

- Detects and Demodulates Transponder Response (FSK)

- Short-Circuit Protection

- Diagnosis

- Sleep-Mode Supply Current: 0.2 mA

- Designed for Automotive Requirements

- 16-Pin SOIC (D) Package

#### DESCRIPTION

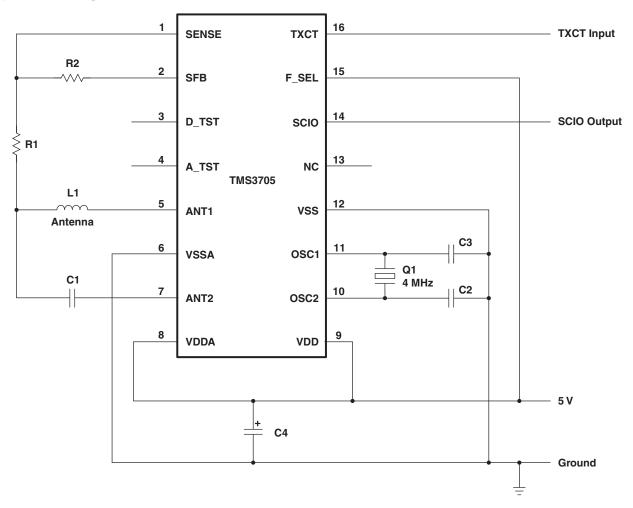

The transponder base station IC is used to drive the antenna of a TI-RFid™ transponder system, to send data modulated on the antenna signal, and to detect and demodulate the response of the transponder. The response of the transponder is a FSK signal (frequency shift keyed). The high or low bits are coded in two different high-frequency signals (134.2 kHz for low bits and 123 kHz for high bits, nominal). The transponder induces these signals in the antenna coil according an internally stored code. The energy the transponder needs to send out the data is stored in a charge capacitor in the transponder. The antenna field charges this capacitor in a preceding charge phase. The IC has an interface to an external microcontroller.

There are two configurations for the clock supply to both the microcontroller and the base station IC:

- Microcontroller and base station IC are supplied with a clock signal derived from only one resonator: The

resonator is attached to the microcontroller. The base station IC is supplied with a clock signal driven by the

digital clock output of the microcontroller. The clock frequency is either 4 MHz or 2 MHz depending on the

selected microcontroller type.

- 2. Both the microcontroller and the base station have their own resonator.

The base station IC has a PLL on-chip that generates a clock frequency of 16 MHz for internal clock supply only. The TMS3705BDRG4 is optimized for higher communication data rates and therefore works without frequency measurement during the write phase.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACK     | AGE <sup>(2)</sup> | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|----------|--------------------|-----------------------|------------------|

| -40°C to 85°C  | SOIC D   | Dool of 2500       | TMS3705A1DRG4         | TMS3705AG4       |

|                | SOIC – D | Reel of 2500       | TMS3705BDRG4          | TMS3705BG4       |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

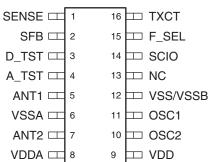

## D PACKAGE (TOP VIEW)

NC - No connection

#### **TERMINAL FUNCTIONS**

|     | TERMINAL |                | DECORPORTION                                                   |  |  |  |  |  |  |

|-----|----------|----------------|----------------------------------------------------------------|--|--|--|--|--|--|

| NO. | NAME     | ITPE           | DESCRIPTION                                                    |  |  |  |  |  |  |

| 1   | SENSE    | Analog input   | Input of the RF amplifier                                      |  |  |  |  |  |  |

| 2   | SFB      | Analog output  | Output of the RF amplifier                                     |  |  |  |  |  |  |

| 3   | D_TST    | Digital output | Test output for digital signals                                |  |  |  |  |  |  |

| 4   | A_TST    | Analog output  | Test output for analog signals                                 |  |  |  |  |  |  |

| 5   | ANT1     | Driver output  | Antenna output 1                                               |  |  |  |  |  |  |

| 6   | VSSA     | Supply input   | Ground for the full bridge drivers                             |  |  |  |  |  |  |

| 7   | ANT2     | Driver output  | Antenna output 2                                               |  |  |  |  |  |  |

| 8   | VDDA     | Supply input   | Voltage supply for the full bridge drivers                     |  |  |  |  |  |  |

| 9   | VDD      | Supply input   | Voltage supply for non-power blocks                            |  |  |  |  |  |  |

| 10  | OSC2     | Analog output  | Oscillator output                                              |  |  |  |  |  |  |

| 11  | OSC1     | Analog input   | Oscillator input                                               |  |  |  |  |  |  |

| 12  | VSS/VSSB | Supply input   | Ground for non-power blocks and PLL                            |  |  |  |  |  |  |

| 13  | NC       |                | Not connected                                                  |  |  |  |  |  |  |

| 14  | SCIO     | Digital output | Data output to the microcontroller                             |  |  |  |  |  |  |

| 15  | F_SEL    | Digital input  | Control input for frequency selection (default value is high)  |  |  |  |  |  |  |

| 16  | TXCT     | Digital input  | Control input from the microcontroller (default value is high) |  |  |  |  |  |  |

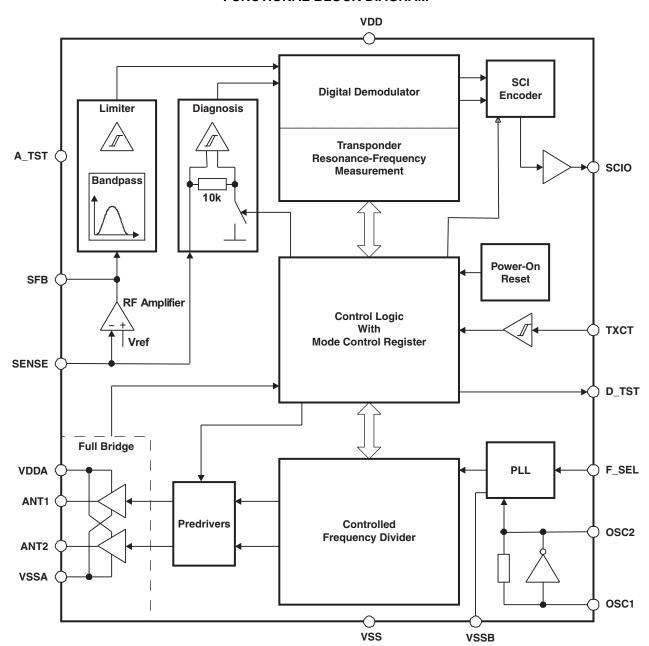

#### **FUNCTIONAL BLOCK DIAGRAM**

## **Power Supply**

The device is supplied with 5 V by an external voltage regulator via two supply pins, one for providing the driver current for the antenna and for supplying the analog part in front of the digital demodulator and one for supplying the other blocks.

The power supply supplies a power-on reset that brings the control logic into idle mode as soon as the supply voltage drops under a certain value.

In sleep mode the sum of both supply currents is reduced to 0.2 mA. The base station device falls into sleep mode 100 ms after TXCT has changed to high. When TXCT changes to low or is low, the base station IC immediately goes into and remains in normal operation.

#### Oscillator

The oscillator generates the clock of the base station IC of which all timing signals are derived. Between its input and output a crystal or ceramic resonator is connected that oscillates at a typical frequency of 4 MHz. If a digital clock signal with a frequency of 4 MHz or 2 MHz is supplied to pin OSC1, the signal can be used to generate the internal operation frequency of 16 MHz.

The oscillator block contains a PLL that generates the internal clock frequency of 16 MHz from the input clock signal. The PLL multiplies the input clock frequency depending on the logic state of the input pin F\_SEL by a factor of 4 (F\_SEL is high) or by a factor of 8 (F\_SEL is low).

In sleep mode the oscillator is switched off.

#### **Predrivers**

The predrivers generate the signals for the four power transistors of the full bridge using the carrier frequency generated by the frequency divider. The gate signals of the p-channel power transistors (active low) have the same width (±1 cycle of the 16 MHz clock), the delay between one p-channel MOSFET being switched off and the other one being switched on is defined to be 12 cycles of the 16 MHz clock. In write mode the first activation of a gate signal after a bit pause is synchronized to the received transponder signal by a phase shift of 18°.

## **Full Bridge**

The full bridge drives the antenna current at the carrier frequency during the charge phase and the active time of the write phase. The minimal load resistance the full bridge sees between its outputs in normal operation at the resonance frequency of the antenna is  $43.3~\Omega$ . When the full bridge is not active, the two driver outputs are switched to ground.

Both outputs of the full bridge are protected independently against short-circuits to ground.

In case of an occurring short-circuit, the full bridge is switched off in less than 10 µs in order to avoid a drop of the supply voltage. After a delay time of less than 10 ms the full bridge is switched on again to test if the short-circuit is still there. An overcurrent due to a resistive short to ground that is higher than the maximum current in normal operation but lower than the current threshold for overcurrent protection does not need to be considered.

### **RF Amplifier**

The RF amplifier is an operational amplifier with a fixed internal voltage reference and a voltage gain of 5 defined by external resistors. It has a high gain-bandwidth product of at least 2 MHz in order to show a phase shift of less than 16° for the desired signal and to give the possibility to use it as a low-pass filter by adapting additional external components.

The input signal of the RF amplifier is DC coupled to the antenna. The amplitude of the output signal of the RF amplifier is higher than 5 mV peak-to-peak.

#### **Band-Pass Filter and Limiter**

The band-pass filter provides amplification and filtering without external components. The lower cut-off frequency is about a factor of 2 lower than the average signal frequency of 130 kHz, the higher cut-off frequency is about a factor of 2 higher than 130 kHz.

The limiter converts the analog sine-wave signal to a digital signal. It provides a hysteresis depending on the minimal amplitude of its input signal. The duty cycle of its digital output signal is between 40% and 60%. The band-pass filter and the limiter together have a high gain of at least 1000.

#### **Diagnosis**

The diagnosis is carried out during the charge phase to detect whether the full bridge and the antenna are working. When the full bridge drives the antenna, the voltage across the coil exceeds the supply voltage so that the voltage at the input of the RF amplifier is clamped by the ESD-protection diodes. For diagnosis, the SENSE pin is loaded on-chip with a switchable resistor to ground so that the internal switchable resistor and the external SENSE resistor form a voltage divider, while the internal resistor is switched off in read mode. When the voltage drop across the internal resistor exceeds a certain value, the diagnosis block passes the frequency of its input signal to the digital demodulator. The frequency of the diagnosis signal is accepted, if eight subsequent time can be detected, all with their counter state within the range of 112 to 125, during the diagnosis time (at most 0.1 ms). The output signal is used during the charge phase only else it is ignored.

When the short-circuit protection switches off one of the full-bridge drivers, the diagnosis also indicates an improper operation of the antenna by sending the same diagnostic byte to the microcontroller as for the other failure mode.

During diagnosis, the antenna drivers are active. In synchronous mode the antenna drivers remain active up to 1 ms after the diagnosis is performed, without any respect to the logic state of the signal at TXCT (thus enabling the microcontroller to clock out the diagnosis byte).

#### **Power-On Reset**

The power-on reset generates an internal reset signal to allow the control logic to start up in the defined way.

#### **Frequency Divider**

The frequency divider is a programmable divider that generates the carrier frequency for the full-bridge antenna drivers. The default value for the division factor is the value 119 needed to provide the nominal carrier frequency of 134.45 kHz generated from 16 MHz. The resolution for programming the division factor is one divider step that corresponds to a frequency shift of about 1.1 kHz. The different division factors needed to cover the range of frequencies for meeting the resonance frequency of the transponder are 114 to 124.

## **Digital Demodulator**

The input signal of the digital demodulator comes from the limiter and is frequency-coded according to the highand low-bit sequence of the transmitted transponder code. The frequency of the input signal is measured by counting the oscillation clock for the time period of the input signal. As the high-bit and low-bit frequencies are specified with wide tolerances, the demodulator is designed to distinguish the high-bit and the low-bit frequency by the shift between the two frequencies and not by the absolute values. The threshold between the high-bit and the low-bit frequency is defined to be 6.5 kHz lower than the measured low-bit frequency and has a hysteresis of ±0.55 kHz.

The demodulator is controlled by the control logic. After the charge phase (that is during read or write phase) it measures the time period of its input signal and waits for the transponder resonance-frequency measurement to determine the counter state for the threshold between high-bit and low-bit frequency. Then the demodulator waits for the occurrence of the start bit. For that purpose, the results of the comparisons between the measured time periods and the threshold are shifted in a 12-bit shift register. The detection of the start bit comes into effect when the contents of the shift register matches a specific pattern, indicating 8 subsequent periods below the threshold immediately followed by 4 subsequent periods above the threshold. A 2-period digital filter is inserted in front of the 12-bit shift register to make a start bit detection possible in case of a non-monotonous progression of the time periods during a transition from low- to high-bit frequency.

The bit stream detected by the input stage of the digital demodulator passes a digital filter before being evaluated. After demodulation, the serial bit flow received from the transponder is buffered byte-wise before being sent to the microcontroller by SCI encoding.

### **Transponder Resonance-Frequency Measurement**

During the pre-bit reception phase, the bits the transponder transmits show the low-bit frequency, which is the resonance frequency of the transponder. The time periods of the pre-bits are evaluated by the demodulator counter. Based on the counter states, an algorithm is implemented that guarantees a correct measurement of the transponder's resonance frequency:

- 1. A time period of the low-bit frequency has a counter state between 112 and 125.

- 2. The measurement of the low-bit frequency (the average of eight subsequent counter states) is accepted during the write mode, when the eight time periods have counter states in the defined range. The measurement during write mode is started with the falling edge at TXCT using the fixed delay time at which end the full bridge is switched on again.

- 3. The counter state of the measured low-bit frequency results in the average counter state of an accepted measurement and can be used to update the register of the programmable frequency divider.

- 4. The measurement of the low-bit frequency (the average of eight subsequent counter states) is accepted during the read mode, when the eight time periods have counter states in the defined range. The start of the measurement during read mode is delayed in order to use a stable input signal for the measurement.

- 5. The threshold to distinguish between high-bit and low-bit frequency is calculated to be by a value of 5 or 7 (see hysteresis in threshold) higher than the counter state of the measured low-bit frequency.

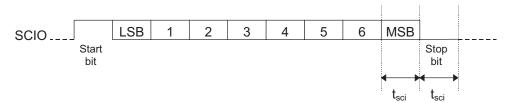

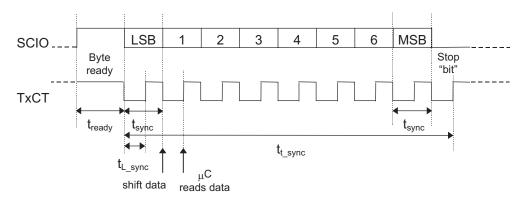

#### SCI Encoder

An SCI encoder performs the data transmission to the microcontroller. As the transmission rate of the transponder is lower than the SCI transmission rate, the serial bit flow received from the transponder is buffered after demodulation and before SCI encoding.

The SCI encoder uses an 8-bit shift register to send the received data byte-wise (least significant bit first) to the microcontroller with a transmission rate of 15.625 kbaud (±1.5 %), one start bit (high) and one stop bit (low), but no parity bit (asynchronous mode indicated by the SYNC bit of the mode control register permanently low). The data bits at the SCIO output are inverted with respect to the corresponding bits sent by the transponder.

The transmission starts after the reception of the start bit. The start byte detection is initialized with the first rising edge. Typical values for the start byte are 81\_H or 01\_H (at SCIO). The start byte is the first byte to be sent to the microcontroller. The transmission stops and the base station returns to idle state when TXCT becomes low or 20 ms after the beginning of the read phase. TXCT remains low for at least 128 µs to stop the read phase and less than 900 µs to avoid starting the next transmission cycle.

The SCI encoder also sends the diagnostic byte 2 ms after beginning of the charge phase. In case of a normal operation of the antenna, the diagnostic byte AF\_H is sent. If no antenna oscillation can be measured or if at least one of the full-bridge drivers is switched off due to a detected short-circuit, the diagnostic byte FF\_H is sent to indicate the failure mode.

The SCI encoder can be switched into a synchronous data transmission mode by setting the mode control register bit SYNC to high. In this mode, the output SCIO indicates by a high state that a new byte is ready to be transmitted. The microcontroller can receive the eight bits at SCIO when sending the eight clock signals (falling edge means active) for the synchronous data transmission via pin TXCT to the SCI encoder.

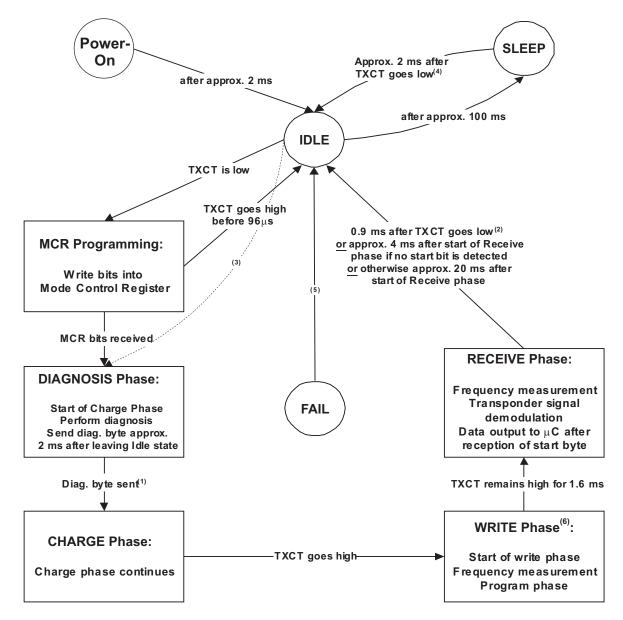

## **Control Logic**

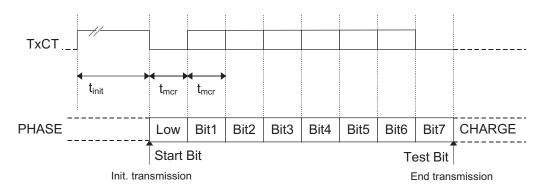

The control logic is the core of the TMS3705 circuit. It contains a sequencer or a state machine that controls the global operations of the base station (see Figure 1). This block has a default mode configuration but can also be controlled by the microcontroller via the TXCT serial input pin to change the configuration and to control the programmable frequency divider. For that purpose a mode control register is implemented in this module that can be written by the microcontroller.

#### Notes:

- (1) In SCI synchronous mode, this transition always occurs approx. 3 ms after leaving Idle state (diag. byte transmission should be completed before).

- (2) A falling edge on TXCT interrupts the Receive phase after a delay of 0.9 ms. TXCT must remain low for at least 128 μs. If TXCT is still low after the 0.9 ms delay, the basestation will go to Idle and directly to the Diagnosis phase one clock cycle later (Dotted line<sup>(3)</sup>).No MCR can be written, by default mode is fully supported in this case. Otherwise, if TXCT returns to high and remains high during the delay, the basestation will stay in Idle and wait for TXCT to go low (this will start properly a new MCR programming) or wait for 100 ms to go to Sleep.

- (3) This transition only occurs in a special case (see note(2))

- (4) A falling edge on TXCT interrupts the Sleep state. Only default mode is fully supported when starting an operation from Sleep with only one falling edge on TXCT (because of the 2 ms delay). For a proper MCR programming, TXCT has to return to high and remain high during this delay.

- (5) Idle mode is the next state in case of undefined sataes ('fail safe state machine')

- (6) Frequency measurement only available for TMS3705A1DRG4

Figure 1. Operational State Diagram for the Control Logic

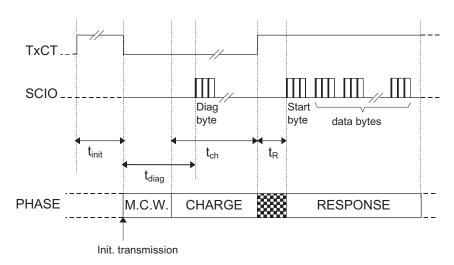

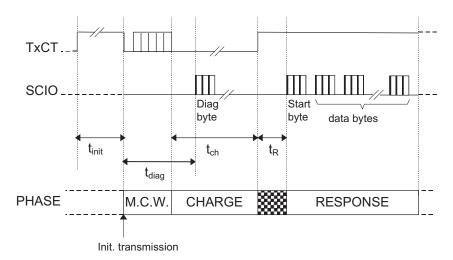

The default mode is a read-only mode that uses the default frequency as the carrier frequency for the full bridge. Therefore the mode control register does not need to be written (it is filled with low states), and the communication sequence between microcontroller and base station starts with TXCT being low for a fixed time to initiate the charge phase. When TXCT becomes high again, the module enters the read phase and the data transmission via the SCIO pin to the microcontroller starts.

There is another read-only mode that differs from the default mode only in the writing of the mode control register before the start of the charge phase. The way that the mode control register is filled and the meaning of its contents is described below.

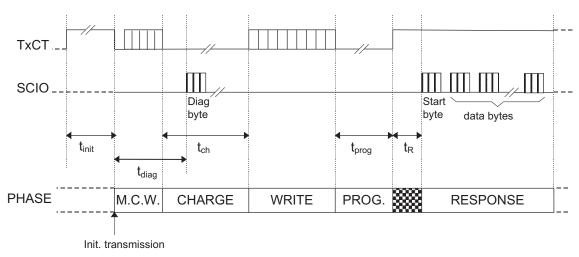

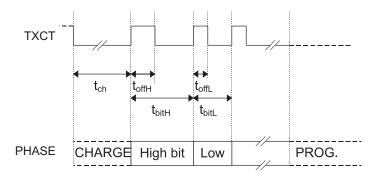

The write-read mode starts with the programming of the mode control register. Then the charge phase starts with TXCT being low for a fixed time. When TXCT becomes high again, the write phase begins in which the data are transmitted from the microcontroller to the transponder via the TXCT pin, the control logic, the predrivers, and the full bridge by amplitude modulation of 100% with a fixed delay time. After the write phase TXCT goes low again to start another charge or program phase. When TXCT becomes high again, the read phase begins.

The contents of the mode control register define the mode and the way that the carrier frequency generated by the frequency divider is selected in order to meet the transponder resonance frequency as good as possible.

| BIT       |       | RESET |                          | DECODIDETION                                                |  |  |  |  |  |

|-----------|-------|-------|--------------------------|-------------------------------------------------------------|--|--|--|--|--|

| NAME NO.  |       | VALUE | DESCRIPTION              |                                                             |  |  |  |  |  |

| START_BIT | Bit 0 | 0     | START_BIT = 0            | The start bit is always low and does not need to be stored. |  |  |  |  |  |

| DATA DITA | Bit 1 | 0     | DATA_BIT[4:1] = 0000     | Microcontroller selects division factor 119                 |  |  |  |  |  |

| DATA_BIT1 | DIL I | U     | DATA_BIT[4:1] = 1111     | Division factor is adapted automatically <sup>(1)</sup>     |  |  |  |  |  |

| DATA BIT2 | Bit 2 | 0     | DATA_BIT[4:1] = 0001     | Microcontroller selects division factor 114                 |  |  |  |  |  |

| DATA_BITZ | DIL Z | U     | DATA_BIT[4:1] = 0010     | Microcontroller selects division factor 115                 |  |  |  |  |  |

| DATA_BIT3 | Bit 3 | 0     | <br>DATA_BIT[4:1] = 0110 | Microcontroller selects division factor 119                 |  |  |  |  |  |

| DATA_BIT4 | Bit 4 | 0     | <br>DATA_BIT[4:1] = 1011 | Microcontroller selects division factor 124                 |  |  |  |  |  |

| SCI SANC  | Bit 5 | 0     | SCI_SYNC = 0             | Asynchronous data transmission to the microcontroller       |  |  |  |  |  |

| SCI_SYNC  | DIL 3 | U     | SCI_SYNC = 1             | Synchronous data transmission to the microcontroller        |  |  |  |  |  |

| DV AEC    | Bit 6 | 0     | $RX\_AFC = 0$            | Demodulator threshold is adapted automatically              |  |  |  |  |  |

| RX_AFC    | סונ ס | 0     | RX_AFC = 1               | Demodulator threshold is defined by DATA_BIT[4:1]           |  |  |  |  |  |

| TECT DIT  | Bit 7 | 0     | TEST_BIT = 0             | No further test bytes                                       |  |  |  |  |  |

| TEST_BIT  | DIL / | U     | TEST_BIT = 1             | Further test byte follows for special test modes            |  |  |  |  |  |

Table 1. Mode Control Register (7-Bit Register)

The TMS3705A1DRG4 can adjust the carrier frequency to the transponder resonance frequency automatically by giving the counter state of the transponder resonance-frequency measurement directly to the frequency divider by setting the first four bits in high state. This setting is not available for TMS3705BDRG4. The other combinations of the first four bits allow the microcontroller to select the default carrier frequency or to use another frequency. The division factor can be selected to be between 114 and 124.

Some bits for testability reasons can be added. The default value of these test bits for normal operation is low. Especially the bit 7 called TEST\_BIT is Low for normal operation; otherwise the base station may enter one of the test modes.

The control logic also controls the demodulator, the SCI encoder, the diagnosis, and especially the transmission of the diagnosis byte during the charge phase.

The state diagram in Figure 1 shows the general behavior of the state machine (note that the state blocks drawn can contain more than one state). All given times are measured from the moment when the state is entered if not specified otherwise.

<sup>(1)</sup> Only available for TMS3705A1DRG4

www.ti.com

## **Test Pins**

The IC has an analog test pin A\_TST for the analog part of the receiver. The digital output pin D\_TST is used for testing the internal logic. Both pins need not be connected in the application.

## ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

| V <sub>DD</sub>     | Supply voltage range                             | VDD, VSS/VSSB, VDDA, VSSA | –0.3 V to 7 V                       |

|---------------------|--------------------------------------------------|---------------------------|-------------------------------------|

| Vosc                | Voltage range                                    | OSC1, OSC2                | -0.3 V to (V <sub>DD</sub> + 0.3) V |

| V <sub>inout</sub>  | Voltage range                                    | SCIO, TXCT, F_SEL, D_TST  | -0.3 V to (V <sub>DD</sub> + 0.3) V |

| I <sub>inout</sub>  | Overload clamping current                        | SCIO, TXCT, F_SEL, D_TST  | -5 mA to 5 mA                       |

| V <sub>ANT</sub>    | Output voltage                                   | ANT1, ANT2                | -0.3 V to (V <sub>DD</sub> + 0.3) V |

| I <sub>ANT</sub>    | Output peak current                              | ANT1, ANT2                | –1.1 A to 1.1 A                     |

| V <sub>analog</sub> | Voltage range                                    | SENSE, SFB, A_TST         | -0.3 V to (V <sub>DD</sub> + 0.3) V |

| I <sub>SENSE</sub>  | SENSE input current                              | SENSE, SFB, A_TST         | -5 mA to 5 mA                       |

| I <sub>SFB</sub>    | Input current in case of overvoltage             | SFB                       | -5 mA to 5 mA                       |

| T <sub>A</sub>      | Operating ambient temperature                    |                           | -40°C to 85°C                       |

| T <sub>stg</sub>    | Storage temperature range                        |                           | −55°C to 150°C                      |

| $R_{\theta JA}$     | Thermal resistance, junction to free air         |                           | 130°C/W                             |

| P <sub>D</sub>      | Total power dissipation at T <sub>A</sub> = 85°C |                           | 0.5 W                               |

| V <sub>ESD</sub>    | ESD protection (MIL STD 883)                     |                           | –2000 V to 2000 V                   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

|                  |                           |                           | MIN                 | NOM | MAX                 | UNIT |

|------------------|---------------------------|---------------------------|---------------------|-----|---------------------|------|

| V <sub>DD</sub>  | Supply voltage            | VDD, VSS/VSSB, VDDA, VSSA | 4.5                 | 5   | 5.5                 | V    |

| f <sub>osc</sub> | Oscillator frequency      | OSC1, OSC2                |                     | 4   |                     | MHz  |

| $V_{IH}$         | High-level input voltage  | F_SEL, TXCT, OSC1         | 0.7 V <sub>DD</sub> |     |                     | V    |

| .,               | Law law line with a line  | TXCT, OSC1                |                     |     | 0.3 V <sub>DD</sub> |      |

| $V_{IL}$         | Low-level input voltage   | F_SEL                     |                     |     | 0.2 V <sub>DD</sub> | V    |

| I <sub>OH</sub>  | High-level output current | SCIO, D_TST               | -1                  |     |                     | mA   |

| I <sub>OL</sub>  | Low-level output current  | SCIO, D_TST               |                     |     | 1                   | mA   |

## **ELECTRICAL CHARACTERISTICS**

$V_{DD} = 4.5 \text{ V}$  to 5.5 V,  $f_{DS} = 4 \text{ MHz}$ ,  $F_{SEL} = \text{high}$ , over operating free-air temperature range (unless otherwise noted)

| PARAMET                                 | ΓER                                                                                                  | TEST CONDITIONS                                                                                                                 | MIN                 | TYP   | MAX                 | UNIT |

|-----------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|---------------------|------|

| Power Su                                | pply (VDD, VSS/VSSB, VDDA, VSSA                                                                      | )                                                                                                                               |                     |       |                     |      |

| I <sub>DD</sub>                         | Supply current                                                                                       | Sum of supply currents in charge phase, without antenna load                                                                    |                     | 8     | 20                  | mA   |

| I <sub>SLEEP</sub>                      | Supply current, sleep mode                                                                           | Sum of supply currents in sleep mode, without I/O currents                                                                      |                     | 0.015 | 0.2                 | mA   |

| Oscillator                              | (OSC1, OSC2)                                                                                         |                                                                                                                                 |                     |       |                     |      |

| g <sub>osc</sub>                        | Transconductance                                                                                     | f <sub>osc</sub> = 4 MHz, 0.5 V <sub>pp</sub> at OSC1                                                                           | 0.5                 | 2     | 5                   | mA/V |

| C <sub>in</sub>                         | Input capacitance at OSC1 (1)                                                                        |                                                                                                                                 |                     |       | 10                  | рF   |

| C <sub>out</sub>                        | Output capacitance at OSC2 <sup>(1)</sup>                                                            |                                                                                                                                 |                     |       | 10                  | pF   |

| Logic Inp                               | uts (TXCT, F_SEL, OSC1)                                                                              | 1                                                                                                                               |                     |       |                     |      |

| _                                       | <b>-</b>                                                                                             | TXCT                                                                                                                            | 120                 |       | 500                 |      |

| $R_{pullup}$                            | Pullup resistance                                                                                    | F_SEL                                                                                                                           | 10                  |       | 500                 | kΩ   |

| Logic Out                               | puts (SCIO, D_TST)                                                                                   | -                                                                                                                               |                     |       |                     |      |

| V <sub>OH</sub>                         | High-level output voltage                                                                            |                                                                                                                                 | 0.8 V <sub>DD</sub> |       |                     | V    |

| V <sub>OL</sub>                         | Low-level output voltage                                                                             |                                                                                                                                 |                     |       | 0.2 V <sub>DD</sub> | V    |

|                                         | e Outputs (ANT1, ANT2)                                                                               | 1                                                                                                                               |                     |       | 55                  |      |

| ΣR <sub>ds_on</sub>                     | Sum of drain-source resistances                                                                      | Full bridge n-channel and p-channel MOSFETs at driver current I <sub>ant</sub> = 50 mA                                          |                     | 7     | 14                  | Ω    |

|                                         | Duty cycle                                                                                           | p-channel MOSFETs of full bridge                                                                                                | 38                  | 40    | 42                  | %    |

| t <sub>on1</sub> /t <sub>on2</sub>      | Symmetry of pulse widths for the p-channel MOSFETs of full bridge                                    |                                                                                                                                 | 96                  |       | 104.5               | %    |

| I <sub>oc</sub>                         | Threshold for overcurrent protection                                                                 |                                                                                                                                 | 220                 |       | 1100                | mA   |

| t <sub>oc</sub>                         | Switch-off time of overcurrent protection                                                            | Short to ground with 3 $\Omega$                                                                                                 | 0.25                |       | 10                  | μs   |

| $t_{doc}$                               | Delay for switching on the full bridge after an overcurrent                                          |                                                                                                                                 | 2                   | 2.05  | 2.1                 | ms   |

| I <sub>leak</sub>                       | Leakage current                                                                                      |                                                                                                                                 |                     |       | 1                   | μΑ   |

| Analog M                                | odule (SENSE, SFB, A_TST)                                                                            |                                                                                                                                 |                     |       |                     |      |

| I <sub>SENSE</sub>                      | Input current                                                                                        | SENSE, In charge phase                                                                                                          | -2                  |       | 2                   | mA   |

| V <sub>DCREF</sub> /<br>V <sub>DD</sub> | DC reference voltage of RF amplifier, related to VDD                                                 |                                                                                                                                 | 9.25                | 10    | 11                  | %    |

| GBW                                     | Gain-bandwidth product of RF amplifier                                                               | At 500 kHz with external components to achieve a voltage gain of minimum 4-mV <sub>pp</sub> and 5-mV <sub>pp</sub> input signal | 2                   |       |                     | MHz  |

| фо                                      | Phase shift of RF amplifier                                                                          | At 134 kHz with external components to achieve a voltage gain of 5-mV <sub>pp</sub> and 20-mV <sub>pp</sub> input signal        |                     |       | 16                  | o    |

| $V_{sfb}$                               | Peak-to-peak input voltage of band pass at which the limiter comparator should toggle <sup>(2)</sup> | At 134 kHz (corresponds to a minimal total gain of 1000)                                                                        | 5                   |       |                     | mV   |

| f <sub>low</sub>                        | Lower cut-off frequency of band-pass filter (3)                                                      |                                                                                                                                 | 24                  | 60    | 100                 | kHz  |

| f <sub>high</sub>                       | Higher cut-off frequency of band-pass filter <sup>(3)</sup>                                          |                                                                                                                                 | 160                 | 270   | 500                 | kHz  |

| $\Delta V_{hys}$                        | Hysteresis of limiter                                                                                | A_TST pin used as input, D_TST pin as output, Offset level determined by bandpass stage                                         | 25                  | 50    | 135                 | mV   |

Specified by design

Specified by design; functional test done for input voltage of 90 mV<sub>pp</sub>. BP filter tested at three different frequencies:  $f_{mid} = 134$  kHz and gain > 30 db;  $f_{low} = 24$  kHz,  $f_{high} = 500$  kHz and attenuation < -3 dB (reference = measured gain at  $f_{mid} = 134$  kHz).

## **ELECTRICAL CHARACTERISTICS (continued)**

$V_{DD} = 4.5 \text{ V}$  to 5.5 V,  $f_{osc} = 4 \text{ MHz}$ ,  $F\_SEL = high$ , over operating free-air temperature range (unless otherwise noted)

| PARAMETER           |                                             | TEST CONDITIONS MIN                    |        | TYP | MAX     | UNIT |

|---------------------|---------------------------------------------|----------------------------------------|--------|-----|---------|------|

| Diagnos             | sis (SENSE)                                 |                                        | ·      |     |         |      |

| I <sub>diag</sub>   | Current threshold for operating antenna (4) |                                        | 80     |     | 240     | μΑ   |

| Phase-L             | ocked Loop (D_TST)                          |                                        | ·      |     |         |      |

| f <sub>pll</sub>    | PLL frequency                               |                                        | 15.984 | 16  | 16.0166 | MHz  |

| Δf/f <sub>pll</sub> | Jitter of the PLL frequency                 |                                        |        |     | 6       | %    |

| Power-0             | On Reset (POR)                              |                                        | ·      |     |         |      |

| V <sub>por_r</sub>  | POR threshold voltage, rising               | V <sub>DD</sub> rising with low slope  | 1.9    |     | 3.5     | V    |

| V <sub>por_f</sub>  | POR threshold voltage, falling              | V <sub>DD</sub> falling with low slope | 1.3    |     | 2.6     | V    |

<sup>(4)</sup> Internal resistance switched on and much lower than external SENSE resistance.

#### **SWITCHING CHARACTERISTICS**

$V_{DD} = 4.5 \text{ V}$  to 5.5 V,  $f_{osc} = 4 \text{ MHz}$ ,  $F\_SEL = high$ , over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                                                    | TEST CONDITIONS                                                                                                          | MIN | TYP  | MAX                   | UNIT |

|-----------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----|------|-----------------------|------|

| t <sub>init min</sub> | Time for TXCT high to initialize a new transmission                                          | From start of the oscillator after power-on or waking up until reaching the idle mode (see Figure 2, Figure 3, Figure 4) | 2   | 2.05 | 2.2                   | ms   |

| t <sub>diag</sub>     | Delay between leaving idle mode and start of diagnosis byte at SCIO                          | Normal operation (see Figure 2, Figure 3, Figure 4)                                                                      | 2   | 2.12 | 2.2                   | ms   |

| t <sub>R</sub>        | Delay between end of charge or end of program and start of transponder data transmit on SCIO | See Figure 2, Figure 3, Figure 4)                                                                                        |     | 3    |                       | ms   |

| t <sub>off</sub>      | Write pulse pause                                                                            | See Figure 6                                                                                                             | 0.1 |      |                       | ms   |

| t <sub>dwrite</sub>   | Signal delay on TXCT for controlling the full bridge                                         | Write mode                                                                                                               | 73  | 79   | 85                    | μs   |

| t <sub>mcr</sub>      | NRZ bit duration for mode control register                                                   | See Figure 5                                                                                                             | 121 | 128  | 135                   | μs   |

| t <sub>sci</sub>      | NRZ bit duration on SCIO                                                                     | Asynchronous mode (see Figure 7)                                                                                         | 63  | 64   | 65                    | μs   |

| t <sub>dstop</sub>    | Low signal delay on TXCT to stop                                                             | Synchronous mode                                                                                                         | 128 |      | 800                   | μs   |

| t <sub>t_sync</sub>   | Total TXCT time for reading data on SCIO                                                     | Synchronous mode (see Figure 8)                                                                                          |     |      | 900                   | μs   |

| t <sub>sync</sub>     | TXCT period for shifting data on SCIO                                                        | Synchronous mode (seeFigure 8)                                                                                           | 4   | 64   | 100                   | μs   |

| t <sub>L_sync</sub>   | Low phase on TXCT                                                                            | Synchronous mode (see Figure 8)                                                                                          | 2   | 32   | t <sub>sync</sub> – 2 | μs   |

| t <sub>ready</sub>    | Data ready for output after SCIO goes high                                                   | Synchronous mode (see Figure 8)                                                                                          | 1   |      | 127                   | μs   |

12

## **TIMING DIAGRAMS**

Figure 2. Default Mode (Read Only, No Writing Into Mode Control Register)

Figure 3. Read-Only Mode (Writing Into Mode Control Register)

## **TIMING DIAGRAMS (continued)**

NOTE: M.C.W.: Mode control write (to write into the mode control register)

PROG.: Program phase of transponder

Figure 4. Write/Read Mode (Writing Into Mode Control Register)

Figure 5. Mode Control Write Protocol (NRZ Coding)

Figure 6. Transponder Write Protocol

## **TIMING DIAGRAMS (continued)**

Figure 7. Transmission on SCIO in Asynchronous Mode (NRZ Coding)

Figure 8. Transmission on SCIO in Synchronous Mode (NRZ Coding) (For Diagnosis Byte and Data Bytes)

## **APPLICATION INFORMATION**

## **Application Diagram**

Figure 9. Application Diagram

## **REVISION HISTORY**

| Revision | Comments                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------|

| SCBS881  | Initial release                                                                                             |

| SCBS881A | Add parameter values for "Full-Bridge Outputs (ANT1, ANT2)" section in Electrical Characteristics (page 10) |

| SCBS881B | Add TMS3705BDRG4 orderable part number (page 1) Add information specific to TMS3705B (page 7 and 8)         |

## PACKAGE OPTION ADDENDUM

3-Mar-2012

#### **PACKAGING INFORMATION**

www.ti.com

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TMS3705A1DRG4    | NRND                  | SOIC         | D                  | 16   | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR          |                             |

| TMS3705BDRG4     | ACTIVE                | SOIC         | D                  | 16   | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-3-260C-168 HR          |                             |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com 14-Jul-2012

## TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

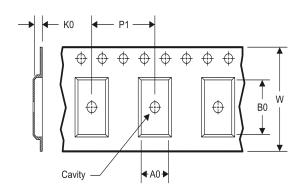

#### **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### TAPE AND REEL INFORMATION

## \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TMS3705A1DRG4 | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

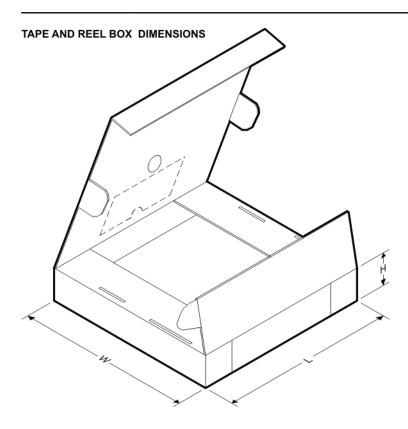

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 14-Jul-2012

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TMS3705A1DRG4 | SOIC         | D               | 16   | 2500 | 367.0       | 367.0      | 38.0        |

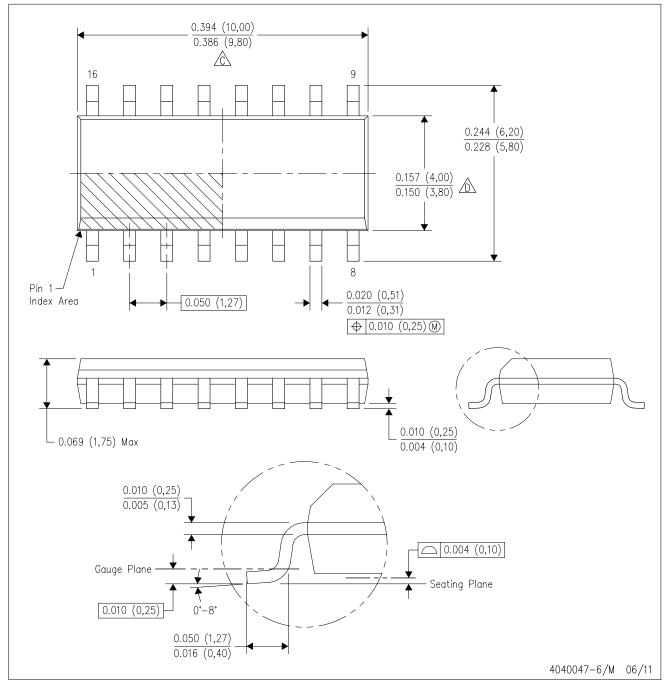

## D (R-PDS0-G16)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AC.

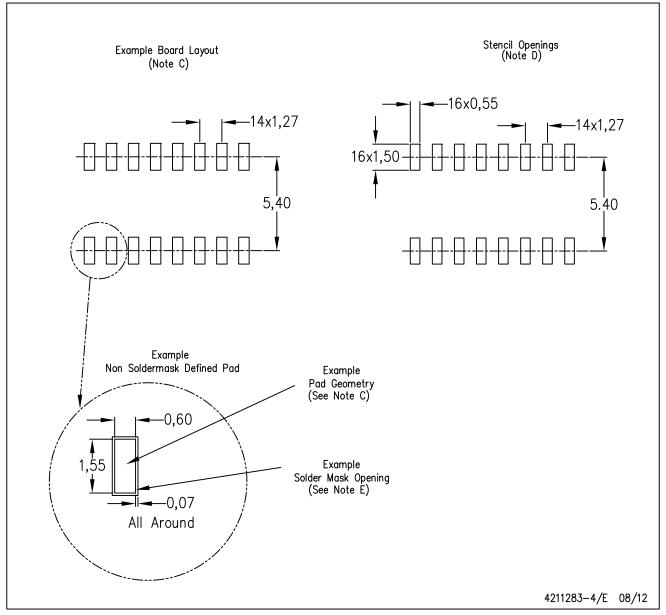

# D (R-PDSO-G16)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| roducts | Applications        |               |

|---------|---------------------|---------------|

| udia    | ununu ti com/ou dio | Automotivo on |

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio www.ti.com/communications **Amplifiers** amplifier.ti.com Communications and Telecom **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** Consumer Electronics www.ti.com/consumer-apps www.dlp.com DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

OMAP Mobile Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity

www.ti-rfid.com

Pr

ооо «ниокрсистемс» - это оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов. Реализуемая нашей компанией продукция насчитывает более полумиллиона наименований.

Благодаря этому наша компания предлагает к поставке практически не ограниченный ассортимент компонентов как оптовыми, мелкооптовыми партиями, так и в розницу.

Благодаря развитой сети поставщиков, помогаем в поиске и приобретении экзотичных или снятых с производства компонентов.

## Наша компания это:

• Гарантия качества поставляемой продукции

Телефон: 8 (495) 268-14-82

Email: n@nsistems.ru

ИНН: 7735154786 ОГРН: 1167746717709

- Широкий ассортимент

- Минимальные сроки поставок

- Техническая поддержка

- Подбор комплектации

- Индивидуальный подход

- Гибкое ценообразование

- Работаем по 275 Ф3