SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

- 58-MHz Max Clock Rate

- Ideal for Waveform Generation and High-Performance State Machine Applications

- 6-Bit Internal Binary Counter

- 8-Bit Internal State Register

- Programmable Clock Polarity

- Outputs Programmable for Registered or Combinational Operation

- 6-Bit Counter Simplifies Logic Equation Development in State Machine Designs

- Programmable Output Enable

#### description

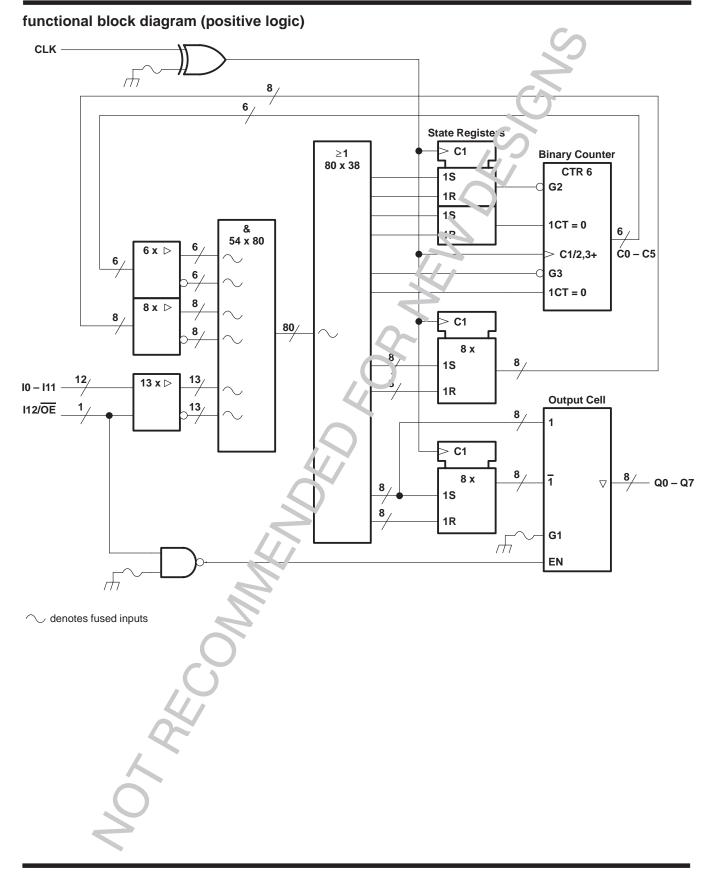

The TIBPSG507AC is a  $13 \times 80 \times 8$ Programmable Sequence Generator (PSG) that offers the system designer unprecedented flexibility in a high-performance field-programmable logic device. Applications such as waveform generators, state machines, dividers, timers, and simple logic reduction are all possible with the PSG. By utilizing the buil-in binary counter, the PSG is capable of generating complex timing controllers. The binary courter also simplifies logic equation development in state machine and waveform generator applications.

The TIBPSG507AC contains 80 product (AND) terms, a 6-bit binary counter with control logic, eight S/R state holding registered and eight outputs. The eight outputs can be individually programmed for either registered or combinational operation. The clock input is fuse programmable for either positive- or negative-edge operation.

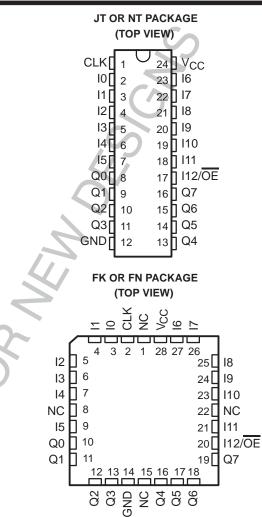

NC - No internal connection

The 6-bit binary counter is controlled by a synchronous-clear and a count/hold function. Each control function has a nonregistered and registered option. When either SCLR0 or SCLR1 is taken high, the counter resets to zero on the next active  $\operatorname{sloc} k$  edge. When either  $\overline{\text{CNT}}/\text{HLD0}$  or  $\overline{\text{CNT}}/\text{HLD1}$  is taken high, the counter is held at the present count and is not allowed to advance on the active clock edge. The SCLR function overrides the  $\overline{\text{CNT}}/\text{HLD1}$  feature the probability of high.

Clock polarity is phorammable through the clock polarity fuse. Leaving this fuse intact selects positive-edge triggering. Negative-edge triggering is selected by blowing this fuse. Pin 17 functions as an input and/or an output enable. When the output enable fuse is intact, all outputs are always enabled allowing pin 17 to be used strictly as an input. Blowing the output enable fuse lets pin 17 function as an output enable and an input. In this mode, the putputs are enabled when pin 17 is low and are in a high-impedance state when pin 17 is high.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

#### description (continued)

The eight outputs can be individually programmed for combinational operation by blowing the output multiplexer fuse. After power up, the device must be initialized to the desired state. When the output multiplexer fuse is left intact, registered operation is selected.

The TIBPSG507AC is characterized for operation from 0°C to 75°C.

#### 6-BIT COUNTER CONTROL FUNCTION TABLE (see Note 1)

| CNT/HLD1 | CNT/HLD0 | SCLR1 | SCLR0 | CPERATION         |

|----------|----------|-------|-------|-------------------|

| L        | L        | L     | L     | cou. te active    |

| Х        | Х        | Х     | н     | syn hronous clear |

| Х        | Х        | н     | х     | synchronous clear |

| Х        | н        | L     | L     | hold counter      |

| Н        | Х        | L     | L     | hold counter      |

NOTE 1: When all fuses are blown on a product line (AND), it sou oper will be high. When all fuses are blown on a sum line (OR), its output will be lot An product and sum terms are low on devices with fuses intact.

| CLK POLARITY FUSE | CLK          | s | R | STATE REGISTER     |

|-------------------|--------------|---|---|--------------------|

| INTACT            | ↑            | L | L | Q <sub>0</sub>     |

| INTACT            | ↑            | L | Н | L                  |

| INTACT            | $\uparrow$   | н | L | Н                  |

| INTACT            | <b>^</b>     | H | Н | INDET <sup>†</sup> |

| BLOWN             |              | L | L | Q <sub>0</sub>     |

| BLOWN             | $\downarrow$ | L | Н | L                  |

| BLOWN             |              | н | L | Н                  |

| BLOWN             | ↓            | Н | Н | INDET <sup>†</sup> |

S/R FUNCTION TABLE ( > e Note 2)

<sup>†</sup>Output state is indeterminate

NOTE 2: After power up, the acvice must be initialized to its desired state. Q<sub>0</sub> is the state of the S/R register before the active clock edge.

INSTRUMENTS POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

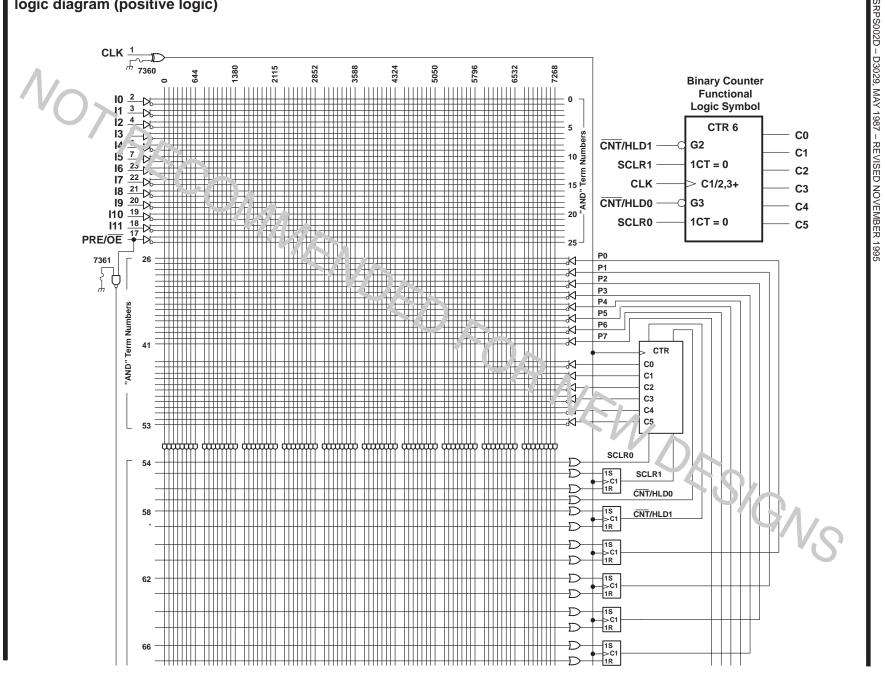

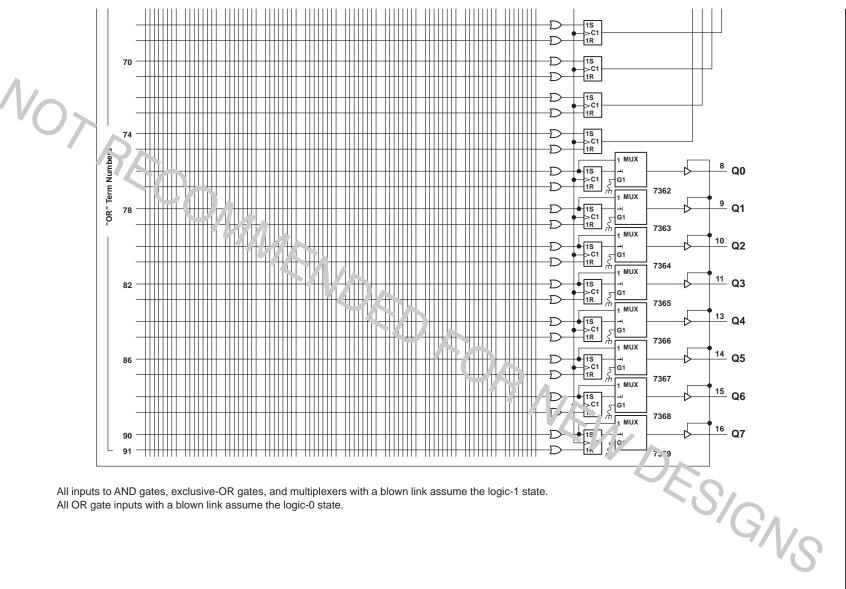

### logic diagram (positive logic)

TIBPSG507AC 13  $\times$  80  $\times$  8 PROGRAMMABLE SEQUENCE GENERATOR

Ь

TEXAS TANK INSTRUMENTS

All OR gate inputs with a blown link assume the logic-0 state.

TIBPSG507AC TIBPSG507AC  $13 \times 80 \times 8$  PROGRAMMABLE SEQUENCE GENERATOR SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

TEXAS TAL INSTRUMENTS POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

-

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 3)<br>Input voltage (see Note 3) |                |

|----------------------------------------------------------------------------|----------------|

| Voltage applied to disabled output (see Note 3)                            | 5.5 V          |

| Operating free-air temperature range                                       |                |

| Storage temperature range                                                  | –65°C to 150°C |

| Storage temperature range                                                  | –65°C to 150°C |

NOTE 3: These ratings apply except for programming pins during a programming cycle or during the diamostic mode.

#### recommended operating conditions

|                 |                                                      |                                  | MIN  | NOM | MAX  | UNIT |  |

|-----------------|------------------------------------------------------|----------------------------------|------|-----|------|------|--|

| VCC             | Supply voltage                                       |                                  | 4.75 | 5   | 5.25 | V    |  |

| VIH             | High-level input voltage                             |                                  | 2    |     | 5.5  | V    |  |

| VIL             | Low-level input voltage                              |                                  |      |     | 0.8  | V    |  |

| ЮН              | High-level output current                            | High-level output current        |      |     | -3.2 | mA   |  |

| IOL             | Low-level output current                             |                                  |      |     | 16   | mA   |  |

| +               | Dulas duration                                       | Clock high                       | 6    |     |      | 20   |  |

| tw              | Pulse duration                                       | Clock low                        | 6    |     |      | ns   |  |

|                 |                                                      | Input or feedback to S/R↑ inputs | 12   |     |      |      |  |

| +               |                                                      | Input or feed' ac' S/R↓ inputs‡  | 19   |     |      |      |  |

| t <sub>su</sub> | Setup time before CLK active transition <sup>†</sup> | Input or fendback to SCLR0       | 20   |     |      | ns   |  |

|                 |                                                      | Input or fedback to CNT/HLD0     | 25   |     |      |      |  |

|                 |                                                      | Input c. feequack at S/R inputs  | 0    |     |      |      |  |

| th              | Hold time after CLK active transition <sup>†</sup>   | Input or . redback at SCLR0      |      |     |      |      |  |

|                 |                                                      | Input or feedback at CNT/HLD0    | 0    |     |      |      |  |

| Τ <sub>Α</sub>  | Operating free-air temperature                       |                                  | 0    | 25  | 75   | °C   |  |

† Internal setup and hold times, t<sub>su</sub> feedback to SCLR1, feedback to CNT/HLD1; th feedback at SCLR1 and feedback at CNT/HLD1, are itar. J. guaranteed by fmax specifications. The active transition of CLK is determined by the programmed state of the CLK polarity fuse.

<sup>‡</sup> See the OR term loading section and Figure 3.

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

| PARAMETER        |                           | TEST CONDITIONS           |               | Mn21 | 1YP† | MAX   | UNIT |

|------------------|---------------------------|---------------------------|---------------|------|------|-------|------|

| VIK              | V <sub>CC</sub> = 4.75 V, | lı = – 18 mA              |               |      |      | -1.2  | V    |

| VOH              | V <sub>CC</sub> = 4.75 V, | I <sub>OH</sub> = -3.2 mA |               | 1.4  | 3.2  |       | V    |

| V <sub>OL</sub>  | V <sub>CC</sub> = 4.75 V, | I <sub>OL</sub> = 16 mA   |               |      | 0.25 | 0.5   | V    |

| IOZH             | V <sub>CC</sub> = 5.25 V, | V <sub>O</sub> = 2.7 V    | C             |      |      | 20    | μA   |

| IOZL             | V <sub>CC</sub> = 5.25 V, | $V_{O} = 0.4 V$           |               |      |      | -20   | μA   |

| lj               | V <sub>CC</sub> = 5.25 V, | V <sub>I</sub> = 5.5 V    |               |      |      | 0.1   | mA   |

| IIH              | V <sub>CC</sub> = 5.25 V, | V <sub>I</sub> = 2.7 V    |               |      |      | 20    | μΑ   |

| IIL              | V <sub>CC</sub> = 5.25 V, | V <sub>I</sub> = 0.4 V    |               |      |      | -0.25 | mA   |

| 10 <sup>‡</sup>  | V <sub>CC</sub> = 5.25 V, | V <sub>O</sub> = 0.5 V    |               | -30  |      | -130  | mA   |

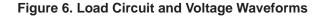

| Icc              | V <sub>CC</sub> = 5.25 V, | See Note 4,               | Outputs of su |      | 156  | 210   | mA   |

| Ci               | f = 1 MHz,                | VI = 2 V                  |               |      | 7    |       | pF   |

| Co               | f = 1 MHz,                | $V_{O} = 2 V$             | 51            |      | 11   |       | pF   |

| C <sub>clk</sub> | f = 1 MHz,                | V <sub>CLK</sub> = 2 V    |               |      | 14   |       | pF   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

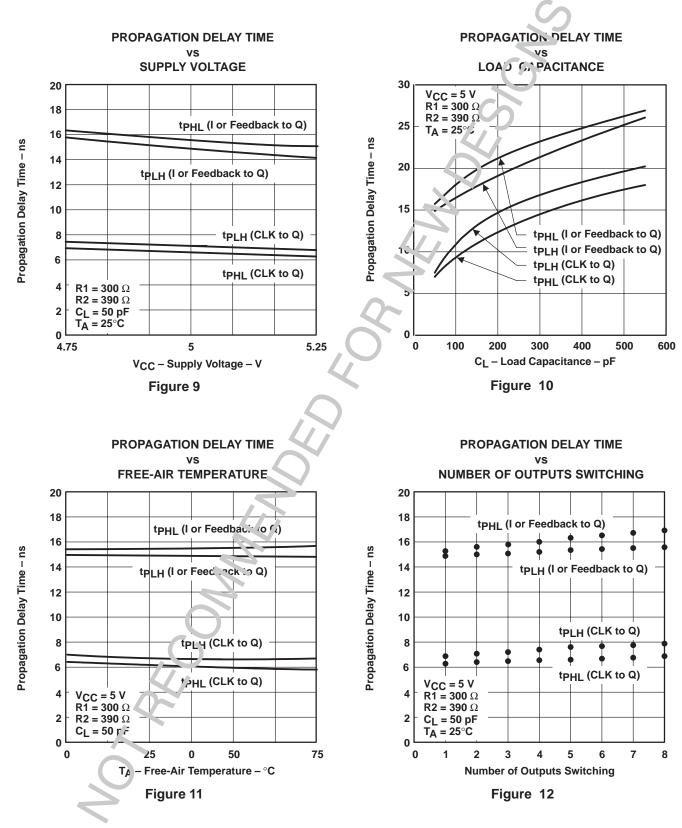

#### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| PARAMETER          | FROM<br>(INPUT)             | TO<br>(OUTPUT)      | TEST CONDITION | MIN | түр† | MAX | UNIT |

|--------------------|-----------------------------|---------------------|----------------|-----|------|-----|------|

|                    | 6-Bit counter with SCLR     | 1 or CNT/HLD1       |                | 58  | 65   |     |      |

| 4 8                | 6-Bit counter with SCLR     | 0                   |                | 40  | 55   |     |      |

| f <sub>max</sub> § | 6-Bit counter with CNT/HLD0 |                     |                | 33  | 50   |     | MHz  |

|                    | With external feedback (    | see Figure 1)       | R1 = 300 Ω,    | 45  | 60   |     |      |

|                    | 011/                        | Q (n unrugistered)# | R2 = 390 Ω,    | 6   |      | 25  |      |

| t <sub>pd</sub> ¶  | CLK                         | کر(*egistered)      | See Figure 6   | 3   |      | 10  | ns   |

|                    | I or Feedback               | (nor egistered)     |                | 6   |      | 20  | ns   |

| ten                | OE↓                         | Q                   |                | 1   | 6    | 10  | ns   |

| <sup>t</sup> dis   | OE↑                         | Q                   |                | 1   | 6    | 10  | ns   |

)The

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . <sup>‡</sup> This parameter approximates I<sub>OS</sub>. The condition  $V_O = 0.5 \text{ V}$  takes tester noise into account. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

§ See the fmax calculations section.

The active edge of CLK is determined by the programmed state of the CLK polarity fuse.  $\# t_{pd}$  CLK to Q (nonregistered) is the same or clata clocked from the counter or state registered.

NOTE 4: When the clock is programm  $x_1$ , regitive edge, then V<sub>1</sub> = 4.5 V. When the clock is programmed for positive edge, then V<sub>1</sub> = 0.

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

#### f<sub>max</sub> calculations

The following are the different speeds that can be achieved when using the TIBPSG50 CC is a state machine. The way the 6-bit counter is controlled will largely determine the operating frequency of the state machine.

$f_{max}$  for a 6-bit counter using SCLR1 or  $\overline{CNT}/HLD1 = \frac{1}{t_{su} + t_{pd}} CLK$  to C where setup time  $t_{su}$  for input or feedback to the S/R inputs = 12 ns and propagation delay time  $t_{pd}$  CLK to Q for the internal S/R registers = 5 ns (difference in  $t_{pd}$  from CLK and feedback, 25 to 20).

Thus:  $f_{max}$  for this condition =  $\frac{1}{(12+5)}$  ns =  $\frac{1}{17}$  = 58 MHz

$f_{max}$  for a 6-bit counter using SCLR0 for reset =  $\frac{1}{t_{su} + t_{pd}}$  CLK  $c_{su}$  where setup time  $t_{su}$  for input or

feedback to the SCLR0 inputs = 20 ns and propagation delay time  $t_{pd}$  CLK to Q for the internal S/R registers = 5 ns (difference in  $t_{pd}$  from CLK and feedback, 25 to 20)

registers = 5 ns (unreference in spu ... Thus:  $f_{max}$  for this condition =  $\frac{1}{(20+5)}$  ns =  $\frac{1}{25}$  ns = \frac{1}{25} ns = \frac{1}{25} ns = \frac{1}{25} ns =  $\frac{1}{25}$  ns = \frac{1}{25} ns =  $\frac{1}{25}$  ns = \frac{1}{25} ns = \frac{1}

$f_{max}$  for a 6-bit counter using  $\overline{CNT}/HLD0$  for reset =  $\frac{1}{t_{SU} + t_{pd}}$  CLK to Q where setup time  $t_{su}$  for input or feedback to  $\overline{CNT}/HLD0 = 25$  ns and propagation delay time  $t_{pd}$  CLK to Q for the internal S/R registers = 5 ns

(difference in tpd from CLK and feedback, 25 to 20).

Thus:  $f_{max}$  for this condition =  $\frac{1}{(25+5)}$  ns =  $\frac{1}{20}$  ns = 33 MHz.

#### programming information

Texas Instruments programmable logic devices can be programmed using widely available software and inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and firmware are available upon request. Information on programmers that are capable of programming Texas Instruments programmable logic is also available, upon request, from the nearest TI sales office, local authorized TI distributor, or by calling Texas Instruments at (214) 997-5666.

Y XY

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

INSTRUMENTS POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

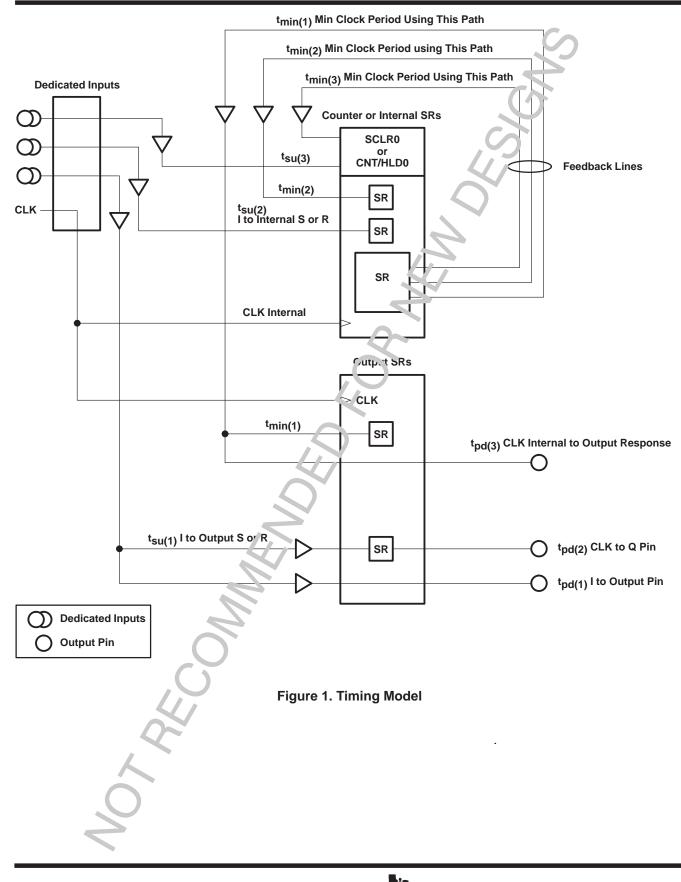

#### glossary — timing model

- tpd<sub>(1)</sub> Maximum time interval from the time a signal edge is received at any input pinds the time any logically affected combinational output pin delivers a response.

- t<sub>pd(2)</sub> Maximum time interval from a positive edge on the clock input pin to data aclivery on the output pin corresponding to any output SR register.

- tpd(3) Maximum time interval from the positive edge on the clock input pin to the response on any logically affected combinational configured output (at the pin), where date or ig n is any internal SR register or counter bit.

- t<sub>su(1)</sub> Minimum time interval that must be allowed between the data any dedicated input and the active clock edge on the clock input pin when data affects the S or R line of any output SR register.

- t<sub>su(2)</sub> Minimum time interval that must be allowed between the data edge on any dedicated input and the active clock edge on the clock input pin when data affects the S or R line of any internal SR register.

- t<sub>su(3)</sub> Minimum time interval that must be allowed between the data edge on any dedicated input and the active clock edge on the clock input pin only when energy data on the CNT/HLD0 line.

- t<sub>su(4</sub>) Minimum time interval that must be allowed between the data edge on any dedicated input and the active clock edge on the clock input pin only when entering data on the SCLR0 line.

- t<sub>min(1)</sub> Minimum clock period (or 1/[maximum frequency]) that the device will accommodate when using feedback from any internal SR register or counter bit to feed the S or R line of any output SR register.

- t<sub>min(2)</sub> Minimum clock period (or 1/[maximum frequency]) that the device will accommodate when using feedback from any internal SR register to reed the S or R line of any internal SR register.

- t<sub>min(3)</sub> Minimum clock period (or 1/[maximum frequency]) that the device will accommodate when using feedback from any internal SR register or counter bit to feed SCLR0 or CNT/HLD0.

#### PARAMETE .? VAL'JES FOR TIMING MODEL

| t <sub>pd(1)</sub> = 20 ns<br>t <sub>pd(2)</sub> = 10 ns<br>t <sub>pd(3)</sub> = 25 ns |          | t <sub>Su</sub> (2) - 12 ns<br>·su(3) = 25 ns | $t_{sl}(1) = 2 \text{ nst}$<br>$t_{su}(2) - 12 \text{ nst}$<br>su(3) = 25  ns<br>$t_{su}(4) = 20 \text{ ns}$ |       | t <sub>min(1)</sub> = 17 ns<br>t <sub>min(2)</sub> = 17 ns<br>t <sub>min(3)</sub> = 25 ns |  |  |  |

|----------------------------------------------------------------------------------------|----------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------|--|--|--|

|                                                                                        |          | INTERNAL                                      | NODE NUMBER                                                                                                  | S     |                                                                                           |  |  |  |

| SCLR0                                                                                  | 25       | CNTHLD0                                       | 28                                                                                                           | P0-P7 | SET 31-38                                                                                 |  |  |  |

| SCLR1                                                                                  | SET 26   | CNTHLD1                                       | SET 29                                                                                                       |       | <b>RESET 39-46</b>                                                                        |  |  |  |

|                                                                                        | RESET 27 |                                               | RESET 30                                                                                                     | Q0-Q7 | <b>RESET 47-54</b>                                                                        |  |  |  |

|                                                                                        |          | C0-C5                                         | 55-60                                                                                                        |       |                                                                                           |  |  |  |

<sup>†</sup> Use  $t_{SU} = 19$  ns for applications where we setup time for S/R $\downarrow$  inputs are required.

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

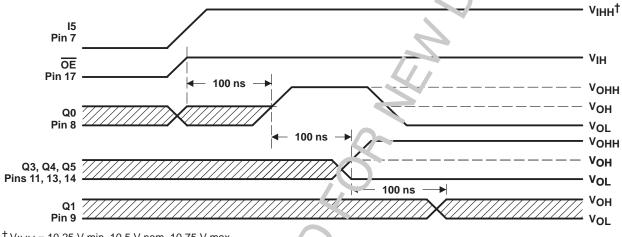

#### diagnostics

A diagnostic mode is provided that allows the user to inspect the contents of the state ragis ters. The following are step-by-step procedures required for the diagnostics.

- Step 1. Disable all outputs by taking pin 17 ( $\overline{OE}$ ) high (see Note 5).

- Step 2. Take pin 8 (Q0) to  $V_{IHH}$  to enable the diagnostics test sequence.

- Step 3. Apply appropriate levels of voltage to pins 11 (Q3), 13 (Q4), and 14 (Q5) to select the desired state register (see Table 1).

The voltage level monitored on pin 9 will indicate the state of the selecter, state register.

NOTE 5: If pin 17 is being used as an input to the array, then pin 7 (I5) must be taken to VIHH before pin 17 is taken high.

<sup>†</sup> VIHH = 10.25 V min, 10.5 V nom, 10.75 V max

Figure 2. Diagnostics Waveforms

|   | REGISTER MARY A |        | ADDRESS | BURIED REGISTER |

|---|-----------------|--------|---------|-----------------|

|   | PIN 11          | PIN'13 | PIN 14  | SELECTED        |

|   | L               | L      | L       | SCLR0           |

|   | L               | L      | Н       | SCLR1           |

|   |                 | L      | HH      | CNT/HLD0        |

|   | L               | Н      | L       | CNT/HLD1        |

|   |                 | Н      | Н       | P0              |

| ( |                 | Н      | HH      | P1              |

|   | L               | HH     | L       | P2              |

| ( | L               | HH     | Н       | P3              |

|   | L               | HH     | HH      | P4              |

|   | Н               | L      | L       | P5              |

|   | Н               | L      | Н       | P6              |

|   | Н               | L      | HH      | P7              |

| K | Н               | Н      | L       | C0              |

|   | Н               | Н      | Н       | C1              |

|   | Н               | Н      | HH      | C2              |

|   | Н               | HH     | L       | C3              |

|   | Н               | HH     | Н       | C4              |

|   | Н               | HH     | HH      | C5              |

|   |                 |        |         |                 |

### Table 1 Addressing State Registers Lung Diagnostics

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

### PRINCIPLES OF OPERATION

#### **PSG** design theory

Most state machine and waveform generator designs can be simplified with the PSC by referencing all or part of each sequence to a binary count. The internal state registers can then be used to hep track of which binary count sequence is in operation, to store input data and keep track of internally generated status bits, or as output registers when connected to a nonregistered output cell. State registers can also be used to expand the binary counter when a larger counter is needed.

Through the use of the binary counter, the number of product lines and s at rrg isters required for a design is usually reduced. In addition, the designer does not have to be concerned about generating wait states where the outputs are unaffected because these can be timed from the binary counter. For detailed information and examples using this design concept, see *A Designer's Guide to the TIBrG6507* applications report.

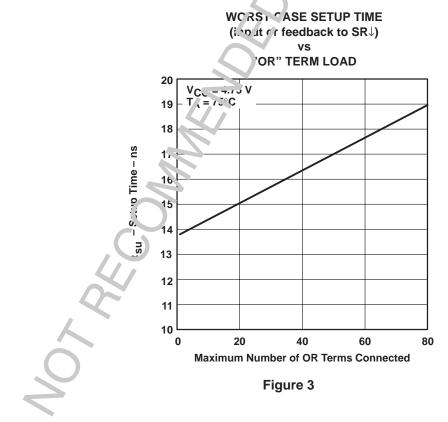

#### **OR term loading**

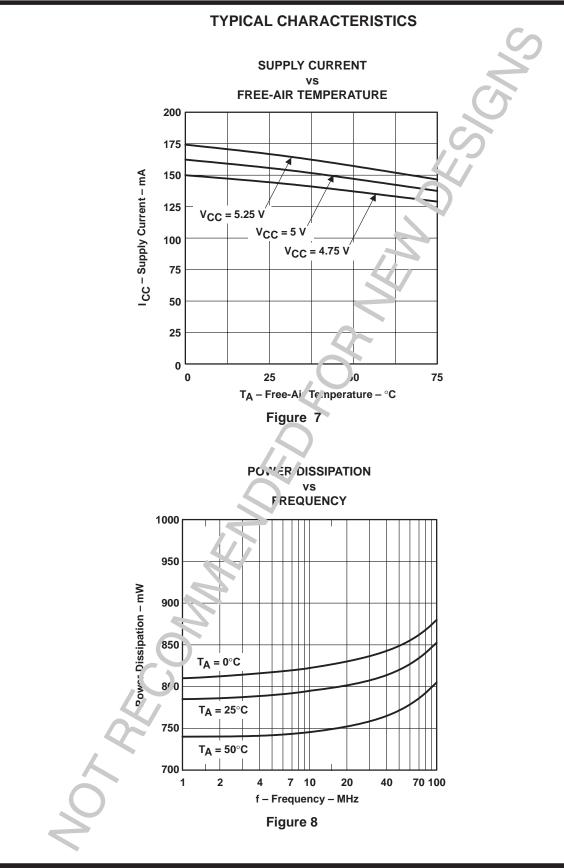

As shown in Figure 3 and by the f<sub>max</sub> calculation, f<sub>max</sub> is affected by the number of terms connected to each OR array line. Theoretically, f<sub>max</sub> is calculated as:

$$f_{max} = \frac{1}{t_{su} + t_{pd}} CLK to Q$$

Since the setup time (input or feedback to S/R $\downarrow$ ) varies with the number of terms connected to each OR array line, (due to capacitance loading) f<sub>max</sub> will also vary. Figure 3 illustrates the relationship between the number of terms connected per OR line and the setup time.

Use Figure 3 to determine the worst-case setup time for a particular application. Identify the OR array line with the maximum number of terms connected. Count the number of terms and use the graph to determine the setup time.

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

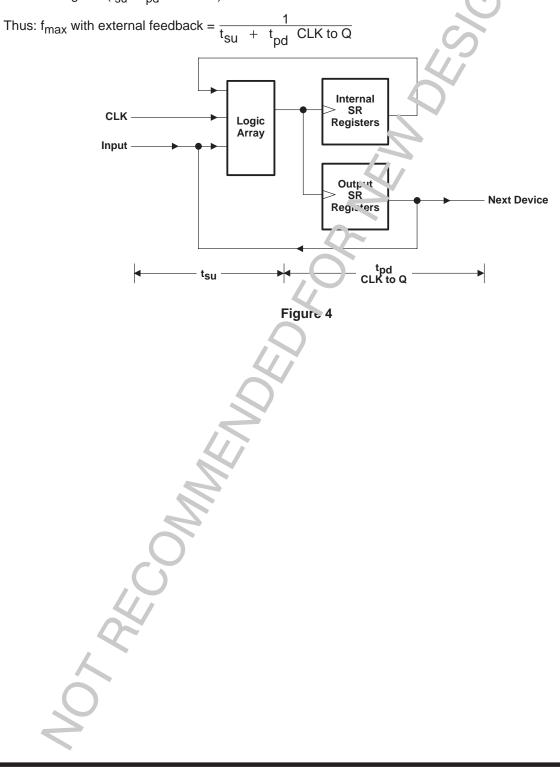

### f<sub>max</sub> with external feedback

The configuration shown is a typical state-machine design with feedback signals set: off-chip. This external feedback could go back to the device inputs or to a second device in a multi-chip state machine. The slowest path defining the clock period is the sum of the clock-to-output delay time and the cetup time for the input or feedback signals ( $t_{su} + t_{pd}$  CLK to Q).

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

### **APPLICATION INFORMATION**

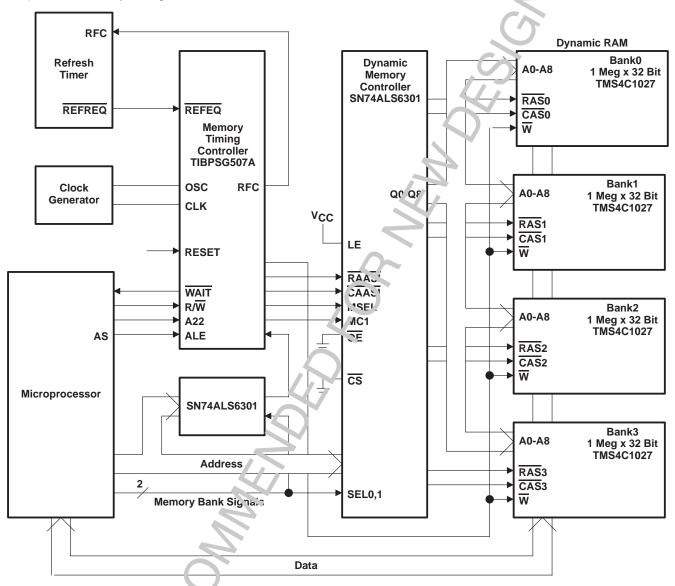

The TIBPSG507AC is used in this application to generate the required memory timing control signals (RAS, CAS, etc.) for the memory timing controller.

For detailed information, please sea the systems Solution for Static Column Decode Application Report.

Figure 5

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

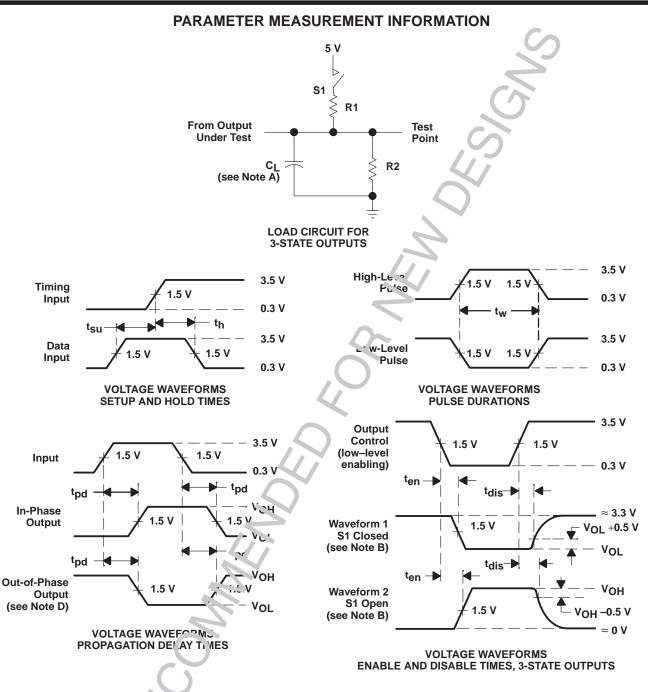

NOTES: A. CL includes probe and jig capacitance and is 50 pF for  $t_{pd}$  and  $t_{en}$ , 5 pF for  $t_{dis}$ .

- B. Waveform 1 is for a. Cutput with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output multimernal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq$  1 MHz, t<sub>f</sub> = t<sub>f</sub>  $\leq$  2 ns, duty cycle = 50%.

- D. When measuring propagation delay times of 3-state outputs, switch S1 is closed.

- E. Equivalent pads may be used for testing.

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

SRPS002D - D3029, MAY 1987 - REVISED NOVEMBER 1995

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

**ООО** «**НИОКРсистемс**» - ЭТО ОПЕРАТИВНЫЕ ПОСТАВКИ ШИРОКОГО СПЕКТРА ЭЛЕКТРОННЫХ КОМПОНЕНТОВ ОТЕЧЕСТВЕННОГО И ИМПОРТНОГО ПРОИЗВОДСТВА НАПРЯМУЮ ОТ ПРОИЗВОДИТЕЛЕЙ И С КРУПНЕЙШИХ МИРОВЫХ СКЛАДОВ. Реализуемая нашей компанией продукция насчитывает более полумиллиона наименований.

Благодаря этому наша компания предлагает к поставке практически не ограниченный ассортимент компонентов как оптовыми, мелкооптовыми партиями, так и в розницу.

Благодаря развитой сети поставщиков, помогаем в поиске и приобретении экзотичных или снятых с производства компонентов.

### Наша компания это:

- Гарантия качества поставляемой продукции

- Широкий ассортимент

- Минимальные сроки поставок

- Техническая поддержка

- Подбор комплектации

- Индивидуальный подход

- Гибкое ценообразование

- Работаем по 275 ФЗ

Телефон: 8 (495) 268-14-82 Email: n@nsistems.ru ИНН: 7735154786 ОГРН: 1167746717709