# **CN8330**

## DS3/E3 Framer with 52 Mbps HDLC Controller

The CN8330 is an integral DS3/E3 framer designed to support the transmission formats defined by ANSI T1.107-1988, T1.107a-1989, T1.404, and ITU-T G.751 standards. All maintenance features required by Bellcore TR-TSY-000009 and AT&T PUB 54014 are provided. In addition, the CN8330 can be optionally configured as a High-Level Data Link Controller (HDLC) usable with or without DS3/E3 framing overhead.

The CN8330 provides framing recovery for M13, C-bit parity, Syntran, and G.751 E3 formatted signals. A First In First Out (FIFO) buffer in the receive path can be enabled to reduce jitter on the incoming data. Transmit and receive data is available to the host in either serial or parallel byte and nibble formats. Access is provided to the terminal data link and the Far End Alarm/Control (FEAC) channel, as specified in T1.107a-1989. Counters are included for frame-bit errors, Line Code Violations (LCVs), parity errors, and Far End Block Errors (FEBEs).

Two operational modes are available: microprocessor and stand-alone monitor control modes. The microprocessor control mode monitors all status conditions and provides configuration control. The stand-alone monitor mode allows the CN8330 to operate as a monitor providing status and alarm information on external pins.

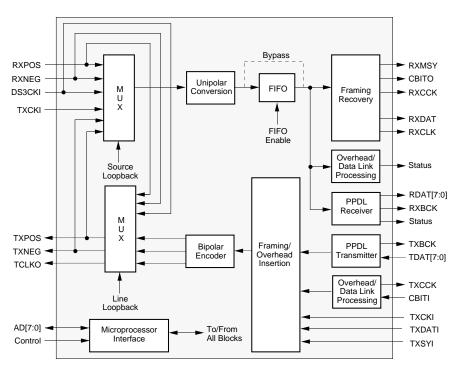

#### **Functional Block Diagram**

#### **Distinguishing Features**

- · Supports DS3/E3 framing modes

- Includes high-speed HDLC controller (52 MHz)

- Framing recovery for M13, C-bit parity, Syntran, and G.751 E3 signals

- Serial or parallel (octet or nibble) interface modes

- Average reframe time of less than 1 ms for DS3 and less than 250 µs for E3

- Supports the LAPD terminal data link and FEAC channel as defined in T1.107a-1989

- 68-pin PLCC or 80-pin MQFP surface-mount package

- Operates from a single +5 VDC ±5% power supply

- Low-power CMOS technology

#### **Applications**

- Digital PCM switches

- Digital Cross-Connect Systems

- · Channel Service Units (CSUs)

- · Channel extenders

- ATM Switches/Concentrators

- PBXs

- Switched Multimegabit Digital Service (SMDS) Equipment

- Test equipment

- · Routers (including HSSI ports)

### **Ordering Information**

| Model Number | Package                                   | Ambient Temperature |

|--------------|-------------------------------------------|---------------------|

| CN8330EPJD   | 68-Pin Plastic Leaded Chip Carrier (PLCC) | –40 to 85° C        |

| CN8330EPD    | 80-Pin Metric Quad Flat Pack (MQFP)       | –40 to 85° C        |

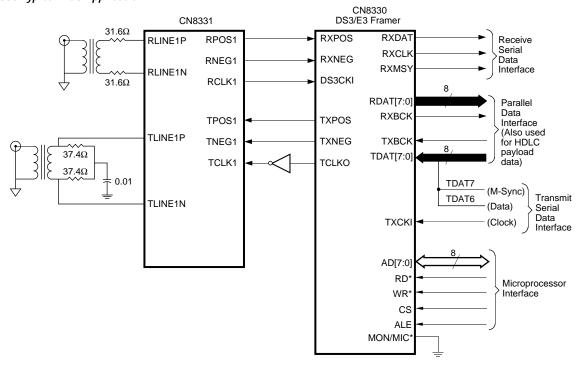

### CN8330 Typical DS3 Application

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The trademarks "Conexant" and the Conexant symbol are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc. Printed in U.S.A. All Rights Reserved

**Reader Response:** Conexant strives to produce quality documentation, and welcomes your feedback. Please send comments and suggestions to conexant.tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

100441E Conexant

# **Table of Contents**

| List of | Figur | es       |                                              |

|---------|-------|----------|----------------------------------------------|

| List of | Table | s        | vi                                           |

| 1.0     | Prod  | uct Des  | cription1-1                                  |

|         | 1.1   | Pin Des  | criptions                                    |

| 2.0     | Func  | tional [ | Description                                  |

|         | 2.1   | Overvie  | w                                            |

|         |       | 2.1.1    | Brief Block Description                      |

|         |       | 2.1.2    | Clock Interface and Initialization           |

|         |       |          | 2.1.2.1 Initialization                       |

|         |       | 2.1.3    | Microprocessor Interface                     |

|         |       |          | 2.1.3.1 Using with Specific Microcontrollers |

|         |       |          | 2.1.3.2 Microprocessor Interrupts2-4         |

|         |       |          | 2.1.3.3 Address Map                          |

|         | 2.2   | Line Int | erfaces                                      |

|         |       | 2.2.1    | Transmitter Line Interface                   |

|         |       | 2.2.2    | Receiver Line Interface                      |

|         | 2.3   | Transmi  | tter Operation                               |

|         |       | 2.3.1    | Input and Synchronization                    |

|         |       | 2.3.2    | DS3 Mode                                     |

|         |       | 2.3.3    | E3 Mode                                      |

|         |       | 2.3.4    | Framing Bit Generation2-10                   |

|         |       | 2.3.5    | Alarm Signal Generation                      |

|         |       | 2.3.6    | Terminal Data Link Transmitter               |

|         |       |          | 2.3.6.1 Sending a Message                    |

|         |       |          | 2.3.6.2 Aborting a Message                   |

|         |       |          | 2.3.6.3 Transmitter Interrupts               |

|         |       |          | 2.3.6.4 Transmitter Control Example          |

|         |       | 2.3.7    | TxFEAC Channel Transmission                  |

|         |       | 2.3.8    | PPDL Transmitter 2-16                        |

|         |       | 2.3.9    | PPDLONLY Mode                                |

|         |       | 2.3.10   | Transmitter Outputs                          |

|         |       | 2.3.11   | Test Equipment Specific Features             |

|     | 2.4 | Receiver Operation                                           | -22 |

|-----|-----|--------------------------------------------------------------|-----|

|     |     | 2.4.1 Bipolar-to-Unipolar Conversion                         | -22 |

|     |     | 2.4.2 Receive FIFO                                           |     |

|     |     | 2.4.3 Received Signal Output                                 | -23 |

|     |     | 2.4.4 Framing Operation                                      | -25 |

|     |     | 2.4.5 Alarm Detection                                        | -25 |

|     |     | 2.4.6 Terminal Data Link Reception                           | -26 |

|     |     | 2.4.6.1 Receiver Interrupts                                  |     |

|     |     | 2.4.6.2 Receiver Response Example                            |     |

|     |     | 2.4.7 RxFEAC Channel Reception                               |     |

|     |     | 2.4.8 PPDL Receiver                                          |     |

|     |     | 2.4.9 PPDLONLY Mode                                          |     |

|     |     | 2.4.10 Serial C-Bit Output                                   | 33  |

|     | 2.5 | Monitor Mode for Stand-Alone Operation                       | -34 |

|     |     | 2.5.1 DS3 Monitor Mode Error Outputs                         | -35 |

| 3.0 | Rea | isters                                                       | 3-1 |

| 0.0 |     |                                                              |     |

|     | 3.1 | Control Registers                                            |     |

|     |     | 0x00—Mode Control Register (CR00)                            |     |

|     |     | 0x01—Terminal Data Link Control Register (CR01)              |     |

|     |     |                                                              |     |

|     |     | 0x03—Transmit FEAC Channel Byte (CR03)                       |     |

|     |     | 0x05—PPDL Control Register (CR05).                           |     |

|     | 2.2 |                                                              |     |

|     | 3.2 | Status Registers                                             |     |

|     |     | 0x10—DS3/E3 Maintenance Status Register (SR00)               |     |

|     |     | 0x11—Counter Interrupt Status Register (SR01)                |     |

|     |     | 0x12—Data Link Interrupt Status Register (SR02)              |     |

|     |     | 0x13—Receive FEAC Chairles Byte (SR03)                       |     |

|     |     | 0x15—Part Number/Hardware Version Register (SR05)            |     |

|     |     | 0x16—Shadow Status Register (SR06)                           |     |

|     |     | 0x20-0x26—DS3/E3 Error Counters                              |     |

|     |     | 0x20—DS3 Parity Error Counter (SR07)                         |     |

|     |     | 0x21—DS3 Disagreement Counter (SR08)                         |     |

|     |     | 0x22—DS3/E3 Frame Error Counter (SR09)                       |     |

|     |     | 0x23—DS3 Path Parity Error Counter (SR10)                    |     |

|     |     | 0x24—DS3 FEBE Event Counter (SR11)                           |     |

|     |     | 0x25,0x26—DS3/E3 LCV Counter—Low and High Bytes (SR12,SR13)  |     |

|     | 3.3 | Memory Registers                                             |     |

|     |     | 0x30–0x37—Transmit Terminal Data Link Message Buffer (TxTDL) |     |

|     |     | 0x40–0x47—Receive Terminal Data Link Message Buffer (RxTDL)  |     |

|     | 3.4 | •                                                            | -15 |

| 4.0   | Mec        | echanical/Electrical Specifications 4-                      |             |  |  |  |  |  |

|-------|------------|-------------------------------------------------------------|-------------|--|--|--|--|--|

|       | 4.1        | Timing Requirements                                         | 4-1         |  |  |  |  |  |

|       | 4.2        | Environmental Conditions                                    | 4-5         |  |  |  |  |  |

|       |            | 4.2.1 Power Requirements and Temperature Range              | . 4-5       |  |  |  |  |  |

|       | 4.3        | Electrical Characteristics                                  | 4-6         |  |  |  |  |  |

|       |            | 4.3.1 DC Characteristics                                    | . 4-6       |  |  |  |  |  |

|       | 4.4        | Mechanical Specifications                                   | 4-8         |  |  |  |  |  |

| Apper | ndix A     | Multimegabit HDLC Formatter                                 | <b>A</b> -1 |  |  |  |  |  |

|       | <b>A.1</b> | Introduction                                                | A-1         |  |  |  |  |  |

|       | <b>A.2</b> | Block and Logic Diagrams                                    | A-3         |  |  |  |  |  |

|       | A.3        | PPDL Transmitter                                            | A-6         |  |  |  |  |  |

|       |            | A.3.1 PPDL Receiver                                         | A-7         |  |  |  |  |  |

| Apper | ndix B     |                                                             | B-1         |  |  |  |  |  |

|       | B.1        | DS3CKI Clock Duty Cycle                                     | B-1         |  |  |  |  |  |

|       | <b>B.2</b> | Overhead Bit Insertion in E3 Parallel Payload Mode          | B-1         |  |  |  |  |  |

|       | B.3        | HDLC Formatter Mode Support While Configured for E3 Framing | B-2         |  |  |  |  |  |

| Annor | win C      |                                                             | C 1         |  |  |  |  |  |

# **List of Figures**

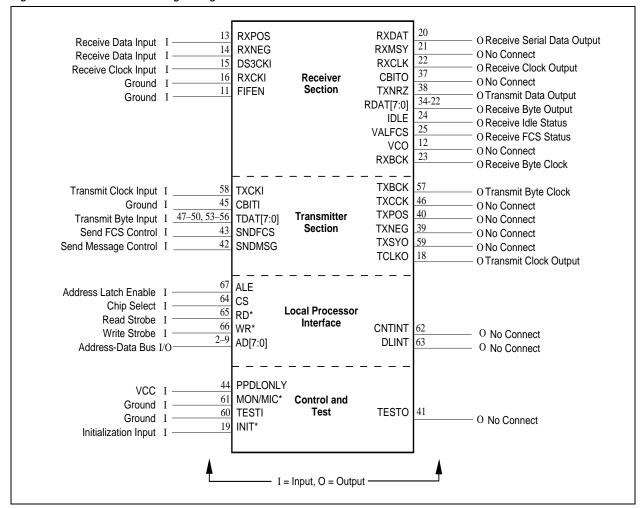

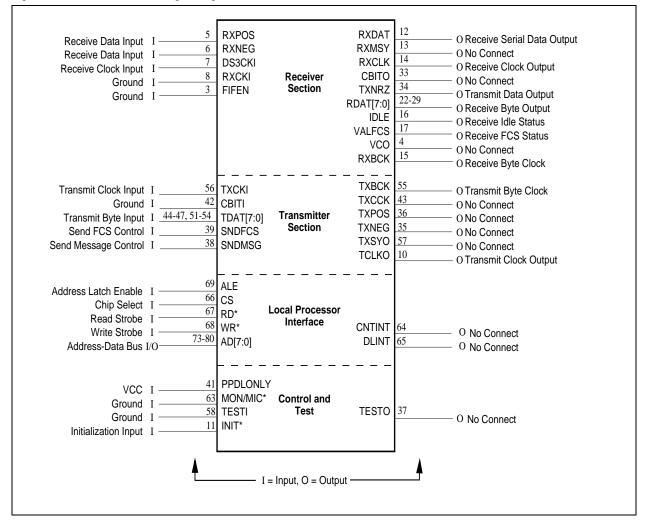

| Figure 1-1.  | CN8330 Pinout Diagram - 68-Pin PLCC                  | 1-3  |

|--------------|------------------------------------------------------|------|

| Figure 1-2.  | CN8330 Pinout Diagram - 80-Pin MQFP                  | 1-4  |

| Figure 1-3.  | CN8330 Framer Functional Logic Diagram - 68-Pin PLCC | 1-6  |

| Figure 1-4.  | CN8330 Framer Functional Logic Diagram - 80-Pin MQFP | 1-7  |

| Figure 2-1.  | Functional Block Diagram                             | 2-2  |

| Figure 2-2.  | Transmitter Line Driver Outputs                      | 2-5  |

| Figure 2-3.  | Clocked Receiver Input                               | 2-6  |

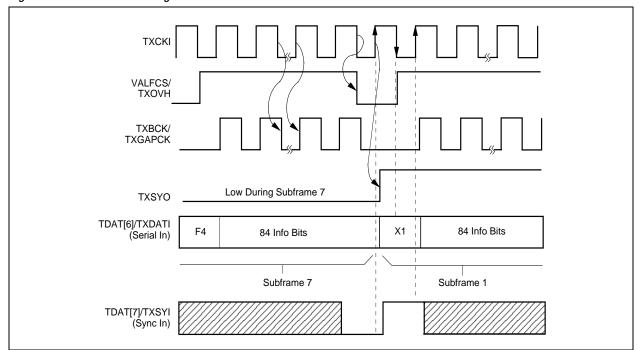

| Figure 2-4.  | Transmitter Timing for Serial DS3 Mode               | 2-8  |

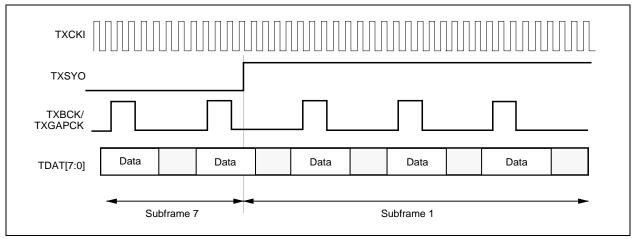

| Figure 2-5.  | Transmitter Timing for Parallel DS3 Mode             | 2-9  |

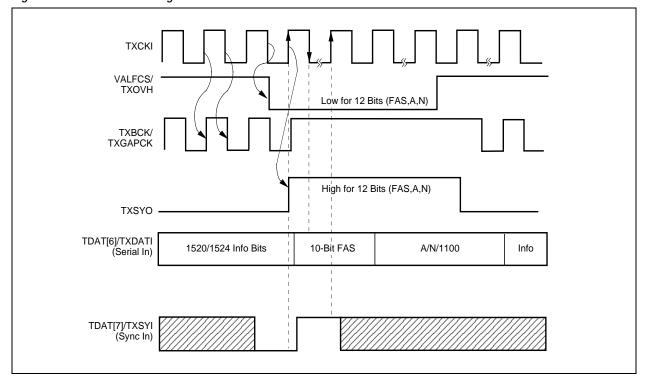

| Figure 2-6.  | Transmitter Timing for Serial E3 Mode                | 2-10 |

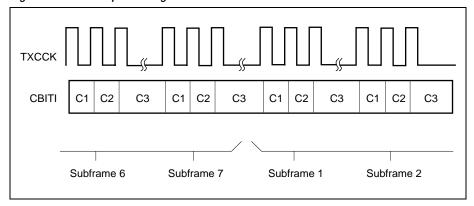

| Figure 2-7.  | C-Bit Input Timing                                   | 2-11 |

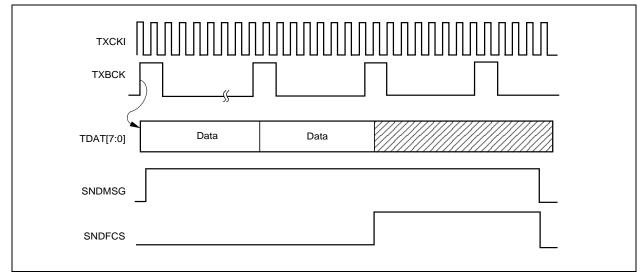

| Figure 2-8.  | PPDL Transmitter Timing                              | 2-17 |

| Figure 2-9.  | Nibble Mode with the PPDLONLY Control Pin Low        | 2-19 |

| Figure 2-10. | VCO Output Signal Timing                             | 2-22 |

| Figure 2-11. | Receiver Timing for Serial DS3 Mode                  | 2-23 |

| Figure 2-12. | Receiver Timing for Parallel DS3 Mode                | 2-24 |

| Figure 2-13. | E3 Receiver Output Timing                            | 2-24 |

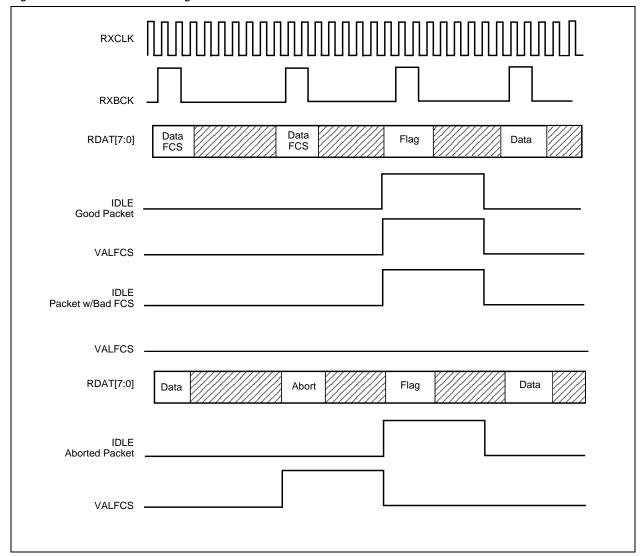

| Figure 2-14. | PPDL Receiver Timing                                 | 2-31 |

| Figure 2-15. | C-Bit Output Timing                                  | 2-33 |

| Figure 2-16. | Monitor Mode Error Indication Timing                 | 2-35 |

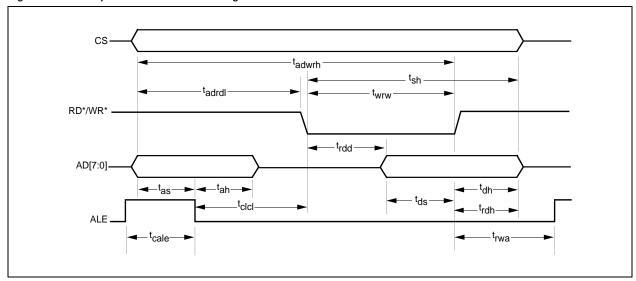

| Figure 4-1.  | Microprocessor Interface Timing                      | 4-2  |

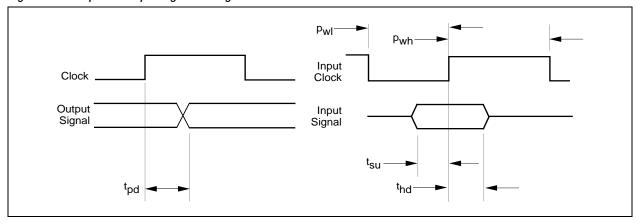

| Figure 4-2.  | Output and Input Signal Timing                       | 4-3  |

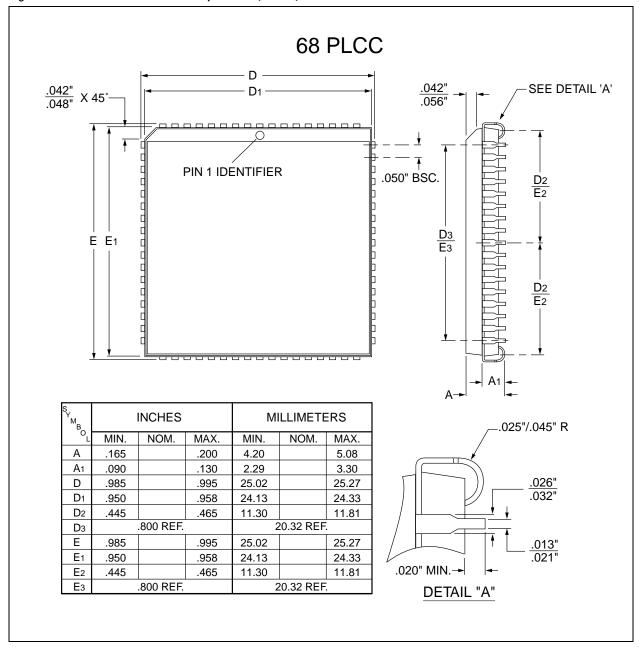

| Figure 4-3.  | 68-Pin Plastic Leaded Chip Carrier (J-Bend)          | 4-8  |

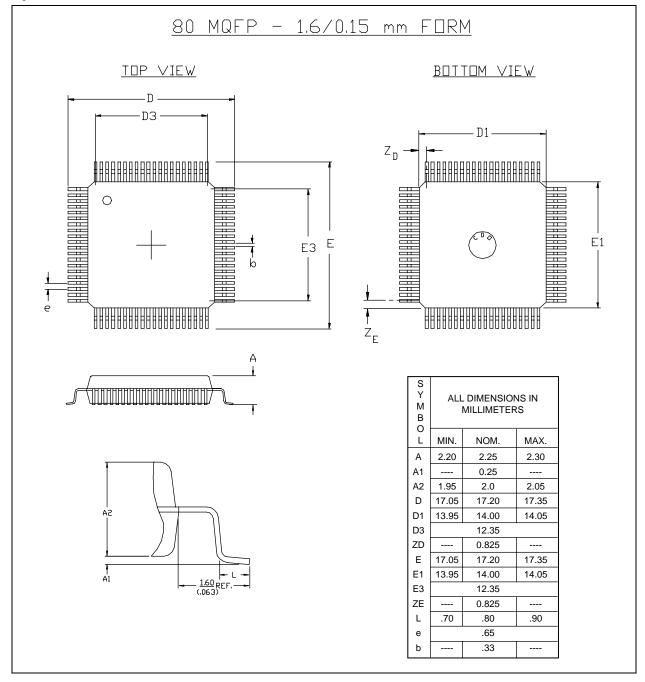

| Figure 4-4.  | 80-Pin Metric Quad Flat Pack (MQFP)                  | 4-9  |

| Figure A-1.  | HDLC Formatter Block Diagram                         | A-2  |

| Figure A-2.  | HDLC Formatter Logic Diagram                         | A-4  |

| Figure A-3.  | HDLC Formatter Logic Diagram - 80-Pin MQFP           | A-5  |

| Figure A-4.  | PPDL Transmitter Timing                              | A-6  |

| Figure A-5.  | PPDL Receiver Timing                                 | A-9  |

List of Figures CN8330

## **List of Tables**

| Table 1-1. | Pin Descriptions                           |

|------------|--------------------------------------------|

| Table 1-2. | Hardware Signal Definitions                |

| Table 2-1. | Transmit Encoding Options                  |

| Table 3-1. | Register Overview                          |

| Table 3-2. | Status Registers                           |

| Table 3-3. | Transmit Terminal Data Link Message Buffer |

| Table 3-4. | Receive Terminal Data Link Message Buffer  |

| Table 4-1. | Microprocessor Interface Timing            |

| Table 4-2. | Clock Timing Requirements                  |

| Table 4-3. | Output Signal Timing                       |

| Table 4-4. | Input Setup/Hold Timing                    |

| Table 4-5. | Absolute Maximum Ratings                   |

| Table 4-6. | DC Characteristics                         |

| Table 4-7. | Output Drive Capability                    |

List of Tables CN8330

## 1.0 Product Description

The CN8330 is a frame synchronization, recovery, and signal generation circuit. Applications for digital terminals include digital cross-connect systems, customer premise multiplexers, channel extenders, network managers, PBXs, Switched Multimegabit Digital Service (SMDS) equipment, and monitor or test equipment. The integrated circuit features a High-Level Data Link Control (HDLC) formatter usable with or without DS3/E3 framing. The CN8330 framer is designed to meet the requirements of DS3 and E3 transmission and reception formats as per ANSI T1.107-1988, T1.107a-1989, T1.404, and ITU-T G.751 standards. Both the LAPD terminal data link and the Far End Alarm Control (FEAC) channel, as defined in T1.107a-1989, are supported. All maintenance features required by Bellcore TR-TSY-000009 and AT&T PUB 54014 are furnished. HDLC data transmission according to ITU-T standard Q.921 and ISO 3309-1984 is supported, as are SMDS standards prETS 300 214 and TR-TSV-000773.

The framer provides framing recovery for M13, C-bit parity, and G.751 E3 formatted signals. The received data stream is available serially for unchannelized applications or for external decoding of the asynchronous multiplexed formats. The framing circuit has an average reframe time of less than 1 msec for DS3 signals and less than 250 µsec for E3 signals. A First In First Out (FIFO) buffer in the receive signal path can be enabled to reduce the jitter on the incoming data. The framer circuitry is capable of operating to 52 MHz, making it compatible with High-Speed Serial Interface (HSSI) signals or DS3 and E3 signals that are embedded in SONET STS-1 or SDH STM-1 carriers.

The transmitter can process serial data from an external pin, or in byte- or nibble-oriented data format from the Payload Parallel Data Link (PPDL) data port. DS3 overhead bits or E3 Frame Alignment Signal (FAS) bits are automatically inserted. The parallel data can be formatted with idle flags, zero stuffing for transparency, and a selectable 16- or 32-bit Frame Check Sequence (FCS). Bytes or nibbles without HDLC formatting can also be transmitted. The transmitter also generates an Alarm Indication Signal (AIS), idle code, yellow alarm, and all-ones signals. DS3 C-bits (or E3 N-bits) can be inserted into the data stream from an external source.

The circuit can be configured as a high-speed data formatter without inserting the CN8330 overhead bits. This allows the circuit to be used for data applications on communication links other than those requiring DS3 or E3 formatting. Data bytes can be formatted with HDLC flags and FCS bytes for transmission at any speed up to 52 MHz.

1.0 Product Description CN8330

DS3/E3 Framer with 52 Mbps HDLC Controller

Configuration, control, and monitoring of the CN8330 termination circuit and framer are accomplished with a selectable microprocessor control mode that monitors all status conditions and provides configuration control. In DS3 mode a stand-alone mode of operation is featured. This allows the circuit to operate as a monitor and provide status and alarm indications to external processing or counting circuitry including:

- AIS, all-ones

- · Yellow alarm

- Loss of signal

- Idle code detection

- Out-of-frame and frame-bit error counting

- Parity error

- LCV (Line Code Violation)

- Path parity

- X-bit disagreement

- FEBE event counting

The received DS3 C-bits (or E3 N-bits) are directed to an external pin to provide visibility for external processing, as required.

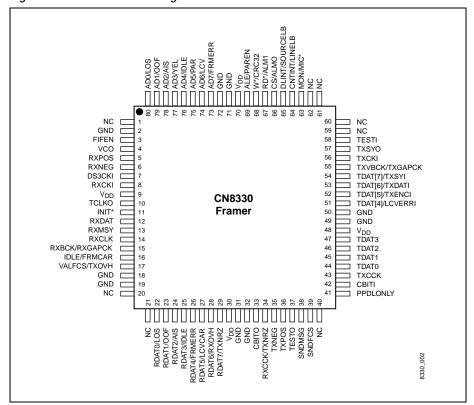

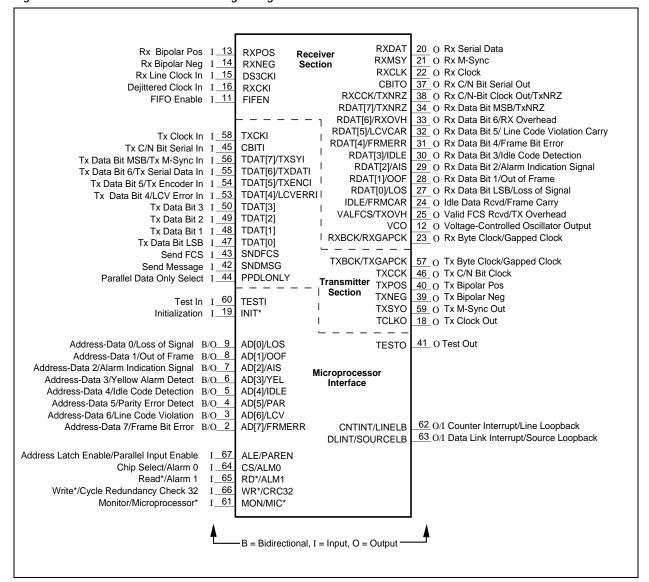

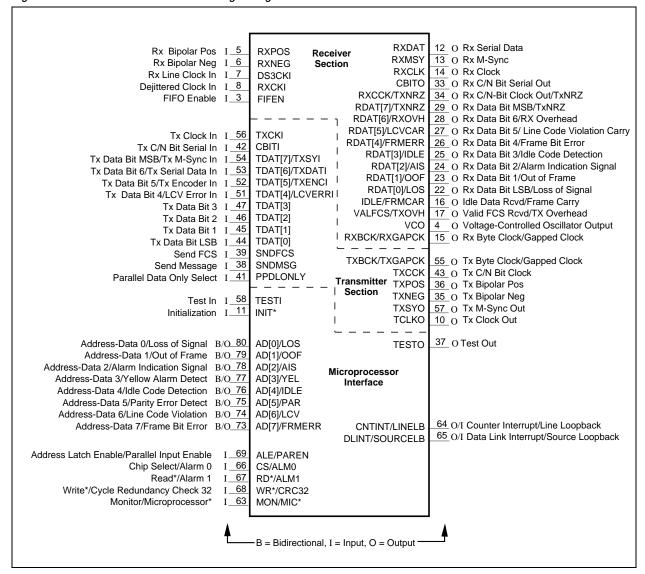

## 1.1 Pin Descriptions

The CN8330 Framer is packaged in a 68-pin Plastic Leaded Chip Carrier (PLCC) and an 80-pin Metric Quad Flat Pack (MQFP) and shown in Figure 1-1 and Figure 1-2 respectively. Pin assignments are listed in numerical order in Table 1-1. Figure 1-3 and Figure 1-4 illustrate functionally partitioned logic diagrams of the CN8330. Pin descriptions, labels, and I/O assignments are detailed in Table 1-2.

68 67 66 65 63 63 63 GND **TESTI FIFEN** 11 59 ☐ TXSYO ⊒ TXCKI vco 12 58 13 TXBCK/TXGAPCK **RXPOS** 57 RXNEG TDAT[7]/TXSYI DS3CKI □ TDAT[6]/TXDATI **RXCKI** ☐ TDAT[5]/TXENCI 17 53 ☐ TDAT[4]/LCVERRI  $V_{DD}$ CN8330 TCLKO 18 □ GND Framer INIT\* 19 51 50 □ V<sub>DD</sub> □ TDAT[3] RXDAT 20 ☐ TDAT[3]

☐ TDAT[2]

☐ TDAT[1]

☐ TDAT[0] RXMSY 21 RXCLK 22 RXBCK/RXGAPCK 23 IDLE/FRMCAR 24 ⊐ тхсск VALFCS/TXOVH CBITI GND ☐ PPDLONLY RDAT[0]/LOS RDAT[1]/OOF RDAT[2]/AID RDAT[3]/IDLE RDAT[4]/FRMERR RDAT[6]/RXOVH RDAT[6]/RXOVH RDAT[6]/RXOVH CBITO

RXCCK/TXNRZ

TXNEG

TXPOS

TESTO

SNDMSG

SNDFCS

Figure 1-1. CN8330 Pinout Diagram - 68-Pin PLCC

1.0 Product Description CN8330

1.1 Pin Descriptions

Figure 1-2. CN8330 Pinout Diagram - 80-Pin MQFP

1.1 Pin Descriptions

Table 1-1. Pin Descriptions

| Pin<br>(68-Pin<br>PLCC) | Pin<br>(80-Pin<br>MQFP) | Pin Label       | 1/0 |

|-------------------------|-------------------------|-----------------|-----|

| 1                       | 72                      | GND             | I   |

| 2                       | 73                      | AD[7]/FRMERR    | B/O |

| 3                       | 74                      | AD[6]/LCV       | B/O |

| 4                       | 75                      | AD[5]/PAR       | B/O |

| 5                       | 76                      | AD[4]/IDLE      | B/O |

| 6                       | 77                      | AD[3]YEL        | B/O |

| 7                       | 78                      | AD[2]/AIS       | B/O |

| 8                       | 79                      | AD[1]/00F       | B/O |

| 9                       | 80                      | AD[0]/LOS       | B/O |

| 10                      | 2                       | GND             | I   |

| 11                      | 3                       | FIFEN           | I   |

| 12                      | 4                       | VCO             | 0   |

| 13                      | 5                       | RXPOS           | I   |

| 14                      | 6                       | RXNEG           | I   |

| 15                      | 7                       | DS3CKI          | I   |

| 16                      | 8                       | RXCKI           | I   |

| 17                      | 9                       | V <sub>DD</sub> | I   |

| 18                      | 10                      | TCLKO           | 0   |

| 19                      | 11                      | INIT*           | I   |

| 20                      | 12                      | RXDAT           | 0   |

| 21                      | 13                      | RXMSY           | 0   |

| 22                      | 14                      | RXCLK           | 0   |

| 23                      | 15                      | RXBCK/RXGAPCK   | 0   |

| 24                      | 16                      | IDLE/FRMCAR     | 0   |

| 25                      | 17                      | VALFCS/TXOVH    | 0   |

| 26                      | 18                      | GND             | I   |

| 27                      | 22                      | RDAT[0]/LOS     | 0   |

| 28                      | 23                      | RDAT[1]/00F     | 0   |

| 29                      | 24                      | RDAT[2]/AIS     | 0   |

| 30                      | 25                      | RDAT[3]/IDLE    | 0   |

| 31                      | 26                      | RDAT[4]/FRMERR  | 0   |

| 32                      | 27                      | RDAT[5]/LCVCAR  | 0   |

| 33                      | 28                      | RDAT[6]/RXOVH   | 0   |

| 34                      | 29                      | RDAT[7]/TXNRZ   | 0   |

| Pin<br>(68-Pin<br>PLCC) | Pin<br>(80-Pin<br>MQFP)            | Pin Label       | I/O |

|-------------------------|------------------------------------|-----------------|-----|

| 35                      | 30                                 | V <sub>DD</sub> | I   |

| 36                      | 31                                 | GND             | I   |

| 37                      | 33                                 | CBITO           | 0   |

| 38                      | 34                                 | RXCCK/TXNRZ     | 0   |

| 39                      | 35                                 | TXNEG           | 0   |

| 40                      | 36                                 | TXPOS           | 0   |

| 41                      | 37                                 | TESTO           | 0   |

| 42                      | 38                                 | SNDMSG          | I   |

| 43                      | 39                                 | SNDFCS          | I   |

| 44                      | 41                                 | PPDLONLY        | I   |

| 45                      | 42                                 | CBITI           | I   |

| 46                      | 43                                 | TXCCK           | 0   |

| 47                      | 44                                 | TDAT[0]         | I   |

| 48                      | 45                                 | TDAT[1]         | I   |

| 49                      | 46                                 | TDAT[2]         | I   |

| 50                      | 47                                 | TDAT[3]         | I   |

| 51                      | 48                                 | $V_{DD}$        | I   |

| 52                      | 49                                 | GND             | I   |

| 53                      | 51                                 | TDAT[4]/LCVERRI | I   |

| 54                      | 52                                 | TDAT[5]/TXENCI  | I   |

| 55                      | 53                                 | TDAT[6]/TXDATI  | I   |

| 56                      | 54                                 | TDAT[7]/TXSYI   | I   |

| 57                      | 55                                 | TXBCK/TXGAPCK   | 0   |

| 58                      | 56                                 | TXCKI           | I   |

| 59                      | 57                                 | TXSY0           | 0   |

| 60                      | 58                                 | TESTI           | I   |

| 61                      | 63                                 | MON/MIC*        | I   |

| 62                      | 64                                 | CNTINT/LINELB   | O/I |

| 63                      | 65                                 | DLINT/SOURCELB  | O/I |

| 64                      | 66                                 | CS/ALM0         | I   |

| 65                      | 67                                 | RD*/ALM1        | I   |

| 66                      | 68                                 | WR*/CRC32       | I   |

| 67                      | 69                                 | ALE/PAREN       | I   |

| 68                      | 70                                 | V <sub>DD</sub> | I   |

|                         | 1,20,<br>21,40,<br>59,60,<br>61,62 | N/C             | _   |

|                         | 19,32,<br>50,71                    | GND             | I   |

1.0 Product Description CN8330

#### 1.1 Pin Descriptions

Figure 1-3. CN8330 Framer Functional Logic Diagram - 68-Pin PLCC

1.1 Pin Descriptions

Figure 1-4. CN8330 Framer Functional Logic Diagram - 80-Pin MQFP

### 1.1 Pin Descriptions

Table 1-2. Hardware Signal Definitions (1 of 5)

|                          | Pin Label | Signal Name                                   | I/O | Definition                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|-----------|-----------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | ALE/PAREN | Address Latch<br>Enable/Parallel Input Enable | I   | A dual-purpose active-high signal which, when MON/MIC* is tied low, is microprocessor-generated and causes the CN8330 to latch in the address on the address-data bus. When MON/MIC* is tied high (stand-alone mode), the parallel input for the PPDL formatter is enabled. When this pin is tied low, transmit data is sourced from the serial input TDAT[6]/TXDAT. <sup>(1)</sup> |

|                          | CS/ALM0   | Chip Select/Alarm 0                           | I   | A dual-purpose signal that enables read/write functions when MON/MIC* is tied low, and controls AIS transmission in stand-alone mode when MON/MIC* is tied high. Both CS and ALM0 are active high signals. (1)                                                                                                                                                                      |

|                          | RD*/ALM1  | Read/Alarm 1                                  | I   | A dual-purpose signal that enables read data to be passed to the address-data bus when MON/MIC* is tied low, and controls idle code transmission in stand-alone mode when MON/MIC* is tied high, RD* is an active low signal and ALM1 is active-high. (1)                                                                                                                           |

| Microprocessor Interface | WR*/CRC32 | Write/Cycle Redundancy<br>Check 32            | I   | A dual-purpose signal that latches write data from the address-data bus when MON/MIC* is tied low, and controls the Cycle Redundancy Check (CRC) when MON/MIC* is tied high. WR* is an active low signal. In stand-alone mode, a high-speed 32-bit CRC calculation is enabled if CRC32 is high; if low, a 16-bit calculation is performed. (1)                                      |

|                          | MON/MIC*  | Monitor/Microprocessor<br>Mode Select         | I   | Selects either microprocessor mode when tied low, or stand-alone monitor mode when tied high. The state of MON/MIC* determines which function the dual-purpose pins (AD[7:0]) serve. The standalone mode is valid only in DS3 mode. (1)                                                                                                                                             |

|                          | AD[0]/LOS | Address-Data 0/Loss of<br>Signal              | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating loss of signal. (1)                                                                                                                                                                                          |

|                          | AD[1]/OOF | Address-Data 1/Out of Frame                   | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating an out-of-frame state. (1)                                                                                                                                                                                   |

|                          | AD[2]/AIS | Address-Data 2/Alarm<br>Indication Signal     | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating alarm indication signal detection. (1)                                                                                                                                                                       |

|                          | AD[3]/YEL | Address-Data 3/Yellow Alarm<br>Detection      | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating a yellow alarm. (1)                                                                                                                                                                                          |

1.1 Pin Descriptions

Table 1-2. Hardware Signal Definitions (2 of 5)

|                          | Pin Label      | Signal Name                              | I/O | Definition                                                                                                                                                                                                                                              |

|--------------------------|----------------|------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | AD[4]/IDLE     | Address-Data 4/Idle Code<br>Detection    | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating an idle code detection. (1)                                                      |

|                          | AD[5]/PAR      | Address-Data 5/Parity Error<br>Detection | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating a parity error. (1)                                                              |

|                          | AD[6]/LCV      | Address-Data 6/Line Code<br>Violation    | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating a line code violation. (1)                                                       |

| rface                    | AD[7]/FRMERR   | Address-Data 7/<br>Frame Bit Error       | B/O | Part of the bidirectional 8-bit multiplexed address-data bus when MON/MIC* is tied low. When in stand-alone mode, this pin is an active-high monitor output indicating a frame bit error. (7)                                                           |

| Microprocessor Interface | CNTINT/LINELB  | Counter Interrupt/<br>Line Loopback      | O/I | The composite interrupt signal generated by the error counters when MON/MIC* is tied low. When MON/MIC* is tied high, this pin controls line loopback transmission in stand-alone mode. CNTINT is an active-low output; LINELB is an active-high input. |

|                          | DLINT/SOURCELB | Data Link Interrupt/Source<br>Loopback   | O/I | The composite interrupt signal generated by the data links when MON/MIC* is tied low. When MON/MIC* is tied high, this pin controls source loopback transmission in stand-alone mode. DLINT is an active-low output; SOURCELB is an active-high input.  |

|                          | TESTI          | Test In                                  | I   | Used for test functions only. Should be tied to ground for normal operation.                                                                                                                                                                            |

|                          | INIT*          | Initialization                           | I   | Active low initialization control. Not all internal storage elements are affected by this signal. See Clock Interface and Initialization in the Overview section of the Functional Description chapter.                                                 |

|                          | TESTO          | Test Out                                 | 0   | Used for test functions only. Should be left disconnected for normal operation.                                                                                                                                                                         |

### 1.1 Pin Descriptions

Table 1-2. Hardware Signal Definitions (3 of 5)

|                     | Pin Label       | Signal Name                                         | I/O | Definition                                                                                                                                                                                                                                            |

|---------------------|-----------------|-----------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | TCLKO           | Transmit Clock Out                                  | 0   | Used to clock out the TXPOS and TXNEG outputs. Data is clocked out on the rising edge of TCLKO.                                                                                                                                                       |

|                     | TXPOS, TXNEG    | Transmit Bipolar<br>Positive, Negative              | 0   | The positive and negative pulses generated by the B3ZS/HDB3 encoder.                                                                                                                                                                                  |

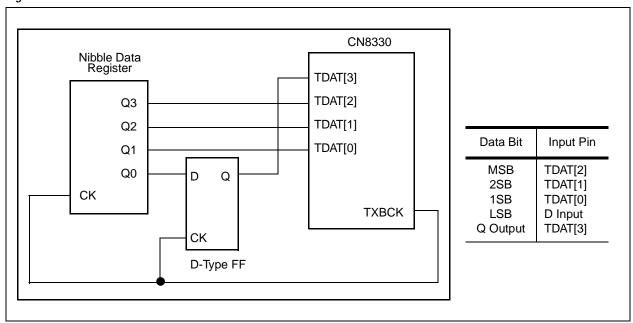

|                     | TDAT[3:0]       | Transmit Data Bits 3–0 (Bit 0 is the LSB)           | I   | In parallel mode <sup>(2)</sup> , these bits form the lower nibble of the byte-oriented data that is input to the PPDL transmitter in response to the transmit byte clock, TXBCK.                                                                     |

| Transmitter Section | TDAT[4]/LCVERRI | Transmit Data Bit 4/Line<br>Code Violation Error In | I   | In parallel mode, the TDAT[4] is bit 4 of the byte-oriented data that is input to the PPDL transmitter. In serial mode, LCVERRI allows test equipment to insert LCVs into the transmit stream under microprocessor control, in both DS3 and E3 modes. |

| Transr              | TDAT[5]/TXENCI  | Transmit Data Bit 5/Transmit<br>Encoder In          | I   | In parallel mode, TDAT[5] is bit 5 of the byte-oriented data that is input to the PPDL transmitter. In serial mode, TXENCI is an alternate direct input to the B3ZS/HDB3 encoder.                                                                     |

|                     | TDAT[6]/TXDATI  | Transmit Data Bit 6/Transmit<br>Serial Data         | I   | In parallel mode, TDAT[6] is bit 6 of the byte-oriented data that is input to the PPDL transmitter. In serial mode, TXDATI is applied to the transmitter.                                                                                             |

|                     | TDAT[7]/TXSYI   | Transmit Data Bit 7/Transmit<br>M-Sync In           | I   | In parallel mode, TDAT[7] is the MSB (Bit 7)of the byte-oriented data that is input to the PPDL transmitter. In serial mode, TXSYI is applied to the transmitter.                                                                                     |

|                     | TXSY0           | Transmit M-Sync Out                                 | 0   | The transmit M-frame sync output.                                                                                                                                                                                                                     |

|                     | TXCKI           | Transmit Clock In                                   | I   | TXCKI rising edge is used to sample parallel data, while the falling edge is used to sample serial data.                                                                                                                                              |

| u                   | TXBCK/TXGAPCK   | Transmit Byte Clock/Gapped<br>Clock                 | 0   | In parallel mode, TXBCK clocks the byte-oriented data that is input to the PPDL transmitter. In serial mode, TXGAPCK is a transmit clock that is gapped during overhead bit intervals in either E3 or DS3 modes.                                      |

| er Section          | SNDMSG          | Send Message                                        | I   | In parallel mode, SNDMSG initiates message transmission in the PPDL transmitter.                                                                                                                                                                      |

| Transmitter Section | SNDFCS          | Send Frame Check Sequence                           | I   | In parallel mode, SNDFCS initiates transmission of the 16- or 32-bit frame check sequence on the PPDC transmitter.                                                                                                                                    |

|                     | CBITI           | Transmit C/N-Bit Serial In                          | I   | The serial C-bit (DS3 mode) or N-bit (E3 mode) data input to be transmitted.                                                                                                                                                                          |

|                     | TXCCK           | Transmit C/N-Bit Clock                              | 0   | Used to sample the CBITI input on the falling edge of TXCCK.                                                                                                                                                                                          |

|                     | PPDLONLY        | Payload Parallel Data Only<br>Select                | I   | Enables the PPDL-only mode in which no DS3/E3 framing is inserted. This mode is entered by tying this pin high.                                                                                                                                       |

1.1 Pin Descriptions

1.0 Product Description

Table 1-2. Hardware Signal Definitions (4 of 5)

|                  | Pin Label     | Signal Name                                    | I/O | Definition                                                                                                                                                                                                                                             |

|------------------|---------------|------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | DS3CKI        | DS3 Receive Line Clock In                      | I   | Clock input DS3CKI should be connected to a 44.736 MHz source (34.368 MHz for the E3) derived from incoming receive data.                                                                                                                              |

|                  | RXPOS, RXNEG  | Receive Bipolar<br>Positive/Negative           | I   | The input positive and negative pulses are sampled on the rising edge of the receiver input clock (DS3CKI) and should be a full clock period wide.                                                                                                     |

|                  | RXCKI         | Receive Dejittered<br>Clock In                 | I   | Used to read the received data out of the internal FIFO (required only if FIFO is enabled). If unused, tie to ground.                                                                                                                                  |

|                  | FIFEN         | FIFO Enable                                    | I   | An active-high input which enables the internal FIFO, used to dejitter the received data by using the dejittered clock input, RXCKI. When FIFEN is low, the FIFO is bypassed and the serial data is output with respect to the incoming clock, DS3CKI. |

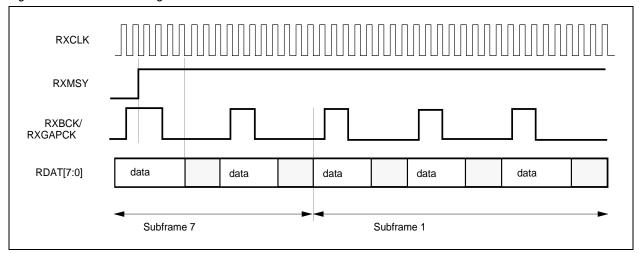

|                  | RXDAT         | Receive Serial Data                            | 0   | RXDAT is the serial data bit stream clocked out on the rising edge of RXCLK.                                                                                                                                                                           |

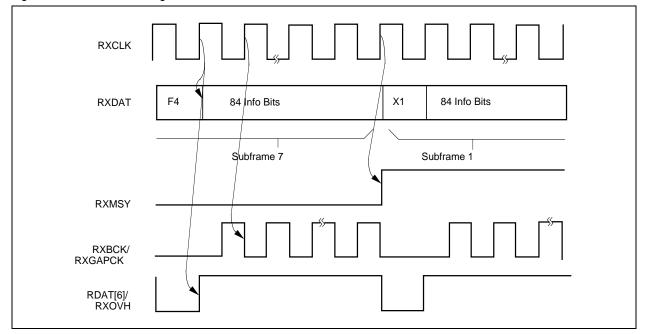

|                  | RXMSY         | Receive M-Sync                                 | 0   | The M-frame synchronization output recovered from the incoming serial data stream.                                                                                                                                                                     |

| ction            | RXCLK         | Receive Clock                                  | 0   | The receive clock used internally to clock out the serial data stream onto RXDAT.                                                                                                                                                                      |

| Receiver Section | RXBCK/RXGAPCK | Receive Byte/Gapped Clock                      | 0   | When in serial mode, RXGAPCK provides a gapped clock signal during every overhead bit (in both DS3 and E3 modes). In parallel mode, RXBCK is used to internally clock out the receive byte-oriented data on RDAT[7:0].                                 |

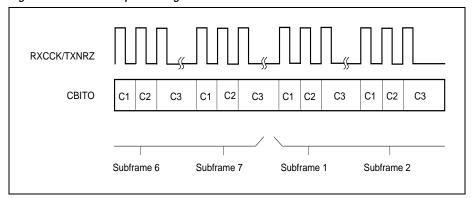

|                  | СВІТО         | Receive C/N-Bit Serial Out                     | 0   | The receive serial C-bit (DS3 mode) or N-bit (E3 mode) data. CBITO changes on the rising edge of RXCCK.                                                                                                                                                |

|                  | RXCCK/TXNRZ   | Receive C/N-Bit Clock<br>Out/Transmit NRZ      | 0   | A clock that indicates transitions in the CBITO signal. In PPDL-only mode, transmit NRZ data is available on this pin.                                                                                                                                 |

|                  | RDAT[0]/LOS   | Receive Data Byte O/Loss of<br>Signal          | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is an active-high monitor output indicating loss of signal.                                                           |

|                  | RDAT[1]/OOF   | Receive Data Byte 1/<br>Out of Frame           | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is an active-high monitor output indicating out-of-frame.                                                             |

|                  | RDAT[2]/AIS   | Receive Data Byte 2/Alarm<br>Indication Signal | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is an active-high monitor output indicating alarm indication signal.                                                  |

1.0 Product Description CN8330

#### 1.1 Pin Descriptions

DS3/E3 Framer with 52 Mbps HDLC Controller

Table 1-2. Hardware Signal Definitions (5 of 5)

|                  | Pin Label          | Signal Name                                       | I/O | Definition                                                                                                                                                                                                      |

|------------------|--------------------|---------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver Section | RDAT[3]/IDLE       | Receive Data Byte 3/Idle<br>Code Detection        | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is an active-high monitor output indicating idle code detection.               |

|                  | RDAT[4]/<br>FRMERR | Receive Data Byte 4/Frame<br>Error Detection      | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is an active-high monitor output indicating frame error detection.             |

|                  | RDAT[5]/<br>LCVCAR | Receive Data Byte 5/Line<br>Code Violation Carry  | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is an active-high ripple carry output from the LCV error counter.              |

|                  | RDAT[6]/RXOVH      | Receive Data Byte 6/Receive<br>Overhead Detection | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is an active-low monitor output indicating the receive overhead bit positions. |

|                  | RDAT[7]/TXNRZ      | Receive Data Byte 7/ Trans-<br>mit NRZ Out        | 0   | Part of the 8-bit data bus output from the PPDL receiver when parallel mode is enabled. When parallel mode is disabled, this pin is a monitor output for the transmit NRZ data.                                 |

|                  | IDLE/<br>FRMCAR    | Idle/Frame Carry                                  | 0   | Set if an idle flag is received after a non-idle sequence, when parallel mode is enabled. When parallel mode is disabled, this pin is an active-high ripple carry output from the frame error counter.          |

|                  | VALFCS/TXOVH       | Valid FCS Received/Transmit<br>Overhead           | 0   | Active high if a valid FCS was received, when parallel mode is enabled. When parallel mode is disabled, this pin is an active-low transmit overhead bit position indicator.                                     |

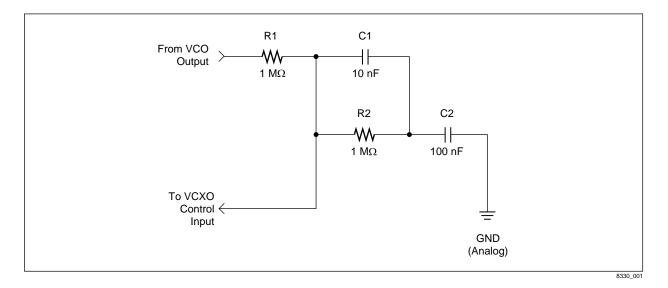

|                  | VCO                | Voltage-Controlled Oscillator<br>Output           | 0   | Used as the phase control for the clock recovery circuit that generates the dejittered clock, RXCKI. Valid only when FIFEN is high. FIFEN enables the internal FIFO when tied high.                             |

| VCC and GND      | V <sub>DD</sub>    | Supply Voltage                                    |     | Four pins are provided for power.                                                                                                                                                                               |

|                  | GND                | Ground                                            |     | Five pins are provided for ground.                                                                                                                                                                              |

| Not Connected    | NC                 | Not Connected                                     |     | These pins are not connected internally.                                                                                                                                                                        |

#### NOTE(S):

- (1) Standalone operation is valid only in DS3 mode.

- Parallel mode is enabled by setting the Parallel Data Enable bit [ParaEn;CR04.3] in the Feature Control Register [CR04; 0x04] when MON/MIC\* is low. When MON/MIC\* is high, Parallel mode is entered by tying the ALE/PAREN pin high.

1-12 **Conexant** 100441E

## 2.0 Functional Description

### 2.1 Overview

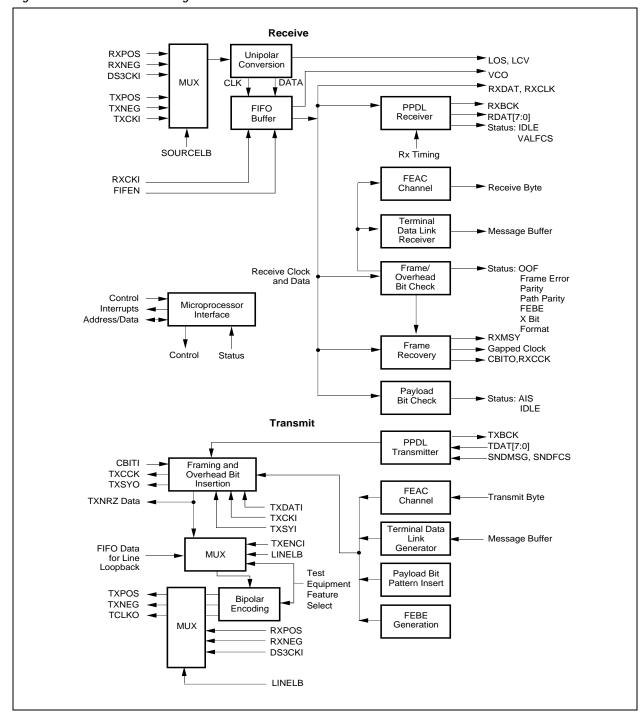

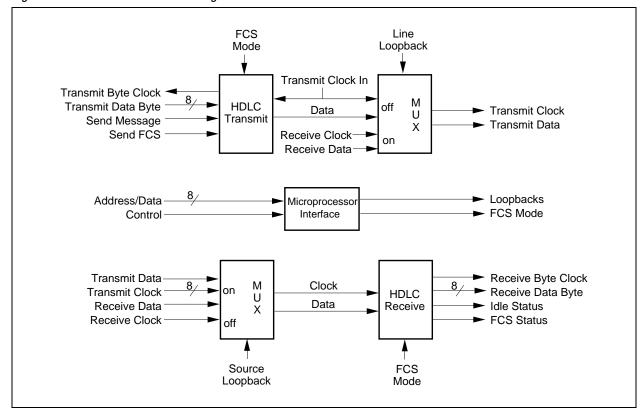

### 2.1.1 Brief Block Description

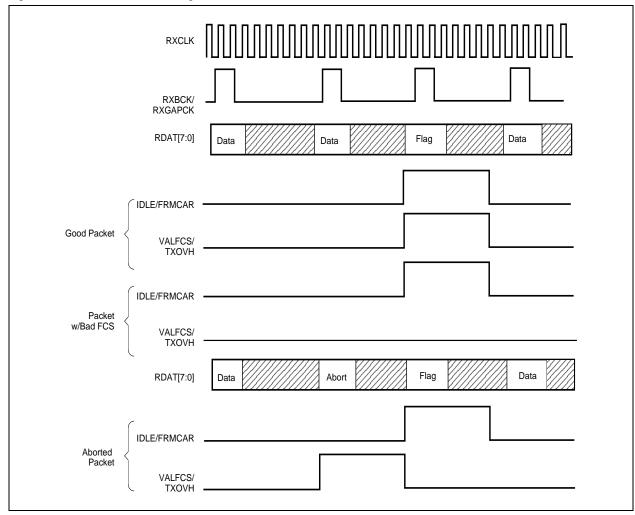

A block diagram of the circuit is illustrated in Figure 2-1. The receive B3ZS/HDB3 signal is decoded and the bipolar input is converted to a unipolar, clocked serial data stream. Frame bit content is checked and the overhead bit data links and alarms are extracted. The receive clock is provided at the receiver output (RXCLK). The data is also connected to a Payload Parallel Data Link (PPDL) receiver that decodes message blocks using the High-Level Data Link Control (HDLC) format (Refer to Appendix A in this document for a description of the HDLC formatter). The recovered data bytes are provided on a parallel output port with a byte clock. The PPDL receiver can also be programmed to operate in nibble mode or transparently without HDLC formatting.

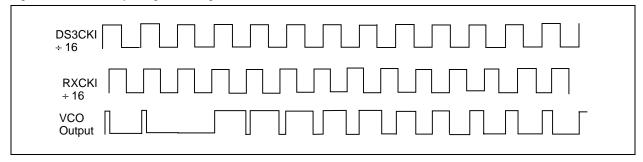

A First In First Out (FIFO) memory buffer in the receive signal path can be enabled to reduce the jitter on the incoming data. The receive data is clocked into the FIFO buffer after bipolar decoding. The FIFO buffer provides a Voltage Controlled Oscillator (VCO) control signal to an external clock recovery circuit. A dejittered clock (RXCKI) from the VCO is then used to read the data from the FIFO buffer to the remaining receiver circuitry.

The transmitter is capable of sending either serial data from an external pin, or byte- or nibble-oriented data from the PPDL data port. DS3 overhead bits or E3 Frame Alignment Signal (FAS) bits are automatically inserted. Parallel data can be formatted with idle flags, zero stuffing for transparency, and a selectable 16- or 32-bit Frame Check Sequence (FCS). Bytes or nibbles without HDLC formatting can also be transmitted. The transmitter is able to send AIS, idle code, yellow alarm, and all-ones signals. DS3 C-bits (or E3 N-bits) can be optionally inserted into the data stream from an external source.

LAPD (Link Access Procedure-D) receiver and transmitter circuitry is provided for the terminal data link in DS3 C-bit parity format and the E3 mode. In C-bit mode, the three C-bits in subframe 5 of the M-frame are used for the terminal data link. In E3 mode, the N-bit is used for the terminal data link.

The microprocessor interface or external outputs monitors all status indications in the received signal. For both DS3 and E3 modes, indications include AIS, all-ones, and yellow alarm detection; and Out-of-Frame (OOF) and frame bit error counting. In addition, loss of signal, idle code, and parity error detection; line code violation (LCV), path parity, and FEBE event counting; and parity and X-bit disagreement counting are provided for DS3 mode. The received DS3 C-bits (or E3 N-bits) are available on an external pin to provide visibility for external processing, if necessary.

#### 2.1 Overview

Figure 2-1. Functional Block Diagram

2.1 Overview

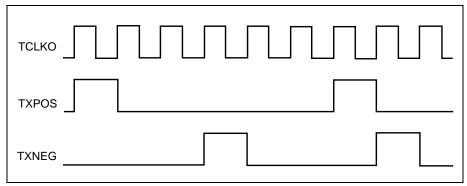

#### 2.1.2 Clock Interface and Initialization

The CN8330 clock input (TXCKI) controls the transmitter. This input should be supplied with a 44.736 MHz clock in DS3 mode and a 34.368 MHz clock in E3 mode. TDAT[6]/TXDATI is sampled on the falling edge of TXCKI and TDAT[7]/TXSYI is sampled on the rising edge of TXCKI. The transmit pulses TXPOS and TXNEG are clocked out on the rising edge of TCLKO.

DS3CKI is the raw data clock that accompanies the RXPOS and RXNEG data pulse inputs for the receiver. If the FIFO buffer is enabled, the data is clocked into the FIFO buffer after B3ZS/HDB3 decoding. RXCKI is the dejittered version of DS3CKI and is used to clock the receive data out of the FIFO buffer (if enabled) to the rest of the receiver circuitry. If the FIFO buffer is disabled, DS3CKI clocks the data into all of the receiver circuitry and the RXCKI input should be grounded.

Clock timing requirements are given in the Electrical and Mechanical Specifications chapter.

#### 2.1.2.1 Initialization

The CN8330 can be initialized with an active-low input pulse of at least 200 ns duration on the INIT\* pin. All error counters are initialized to zero when this input is active low if the transmit and receive clocks are present. Initialization is not required for proper operation. During initialization (active low) host cannot read or write any CN8330.

### 2.1.3 Microprocessor Interface

The CN8330 can be controlled by a microprocessor or a microcontroller through an 8-bit multiplexed address/data interface. An interface to an Intel 8051 family processor or equivalent, or Motorola 68HC11 family or equivalent is provided. The microprocessor interface is enabled by tying the MON/MIC\* pin low. The CN8330 is connected to the microprocessor exactly like static RAM.

### 2.1.3.1 Using with Specific Microcontrollers

The microprocessor interface is designed to allow direct connection of Intel 8051 family, Motorola 68HC11 family, or equivalent microcontrollers. The controller interface to the CN8330 consists of 14 pins: Address Latch Enable (ALE), Read Enable (RD\*), Write Enable (WR\*), Chip Select (CS), eight multiplexed address/data bits (AD[7:0]), and two interrupts (DLINT/SOURCELB and CNTINT/LINELB). If a 68HC11 controller is used, then its address strobe as is connected to ALE, Enable is connected to RD\*, and Read/Write\* (R/W\*) is connected to WR\*. The chip select input (CS/ALM0) allows the control of multiple ICs from a single microprocessor. Interrupt outputs are used for data link and maintenance operations and provide active-low interrupts.

#### 2.1 Overview

## 2.1.3.2 Microprocessor Interrupts

There are two separate interrupt pins that can be connected to the microprocessor (or microcontroller): Counter and Data Link. The counter interrupt pin (CNTINT/LINELB) combines seven sources of interrupts on an external pin connected to the microprocessor. This interrupt signal is active low and is a composite indication of all interrupt sources that are enabled in the Status Interrupt Control Register [CR02;0x02]. The interrupt source can be determined by reading the Counter Interrupt Status Register [SR01;0x11]. The data link interrupt pin (DLINT/SOURCELB) is a composite indication of the interrupts from four sources. The interrupt source can be determined by reading the Data Link Interrupt Status Register [SR02;0x12]. When the C-Bit Parity Mode/Enable DLINT bit [CBitP/DL;CR00.0] is not set, the DLINT/SOURCELB pin is held high (inactive). The two interrupt pins are open-drain outputs and can be connected to form a single-wire ORed interrupt, if desired.

#### 2.1.3.3 Address Map

The register address map for the CN8330 is given in Table 3-1 through Table 3-4, Register Summary. There are three types of registers: Control Registers, which can be read or written; Status Registers and Counters which can only be read; and Data Link Message Buffers which can be read or written. The Control Registers serve as latches that are modified by a microprocessor write operation and can also be read to verify contents. They are located at addresses 0x00-0x05. Status Registers are located at addresses 0x10-0x16. Maintenance Error Counters are located at addresses 0x20-0x26. The Transmit Terminal Data Link Message Buffers are located at addresses 0x30-0x37, and the Receive Terminal Data Link Message Buffers are located at addresses 0x40-0x47. The chip select input (CS/ALM0) must be high to address the CN8330 and to enable read or write operations.

## 2.2 Line Interfaces

#### 2.2.1 Transmitter Line Interface

The transmitted line signals are shown in Figure 2-2. Nine bits of a representative output sequence are shown. Separate signal pins provide the appropriate output signal for positive and negative pulses. The outputs are a full clock period wide and change on positive clock transitions of the TCLKO pin. For additional information on the TXPOS and TXNEG outputs refer to Transmitter Outputs in the Transmitter Operation section in this chapter

B3ZS/HDB3 encoding is performed automatically on the output data stream; however, this encoding can be disabled to send AMI data without any zero code suppression. Transmit NRZ data, prior to B3ZS/HDB3 encoding, is also available on the RDAT[7]/TXNRZ pin when parallel mode is not selected and on the RXCCK/TXNRZ pin when PPDLONLY mode is selected.

Figure 2-2. Transmitter Line Driver Outputs

2.2 Line Interfaces

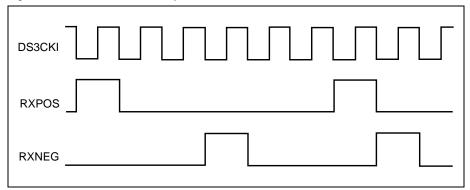

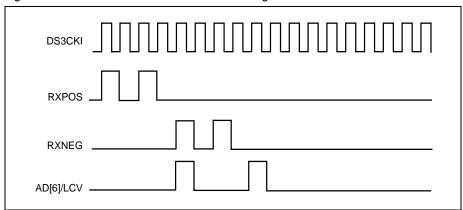

#### 2.2.2 Receiver Line Interface

The line interface for the receive bipolar signals consists of two logic-level signals that represent the positive and negative bipolar line pulses (RXPOS, RXNEG) and an input (DS3CKI) for an externally derived clock at a nominal frequency of 44.736 MHz or 34.368 MHz. The receiver line signals are shown in Figure 2-3. Nine bits of a representative input sequence are shown. The input signal is sampled on the rising edge of the clock signal. B3ZS/HDB3 decoding is provided internally. Decoding can be defeated for NRZ inputs by connecting the NRZ data input to both the RXPOS and RXNEG inputs or by selecting the AMI mode/LCV Type 2 bit [AMI/LCV2;CR04.6] in the Feature Control Register [CR04;0x04].

Figure 2-3. Clocked Receiver Input

2.3 Transmitter Operation

## 2.3 Transmitter Operation

The transmitter circuit is synchronized to the transmit input data by an external synchronization signal. The external synchronization signal sets the M-frame reference for transmitted signals.

### 2.3.1 Input and Synchronization

The input to the transmitter consists of the transmit serial data input (or the PPDL transmitter data), transmit clock, and transmit M-frame sync signal. An M-frame sync signal output is available on the TXSYO pin to synchronize external circuitry, if desired. If an input sync is not provided, the CN8330 generates a sync internally whose position is indicated by TXSYO. In this case, the sync input should be grounded. The TDAT[7]/TXSYI is sampled on the rising edge of TXCKI and TDAT[6]/TXDATI is sampled by the falling edge of TXCKI.

#### 2.3.2 DS3 Mode

The input bits are synchronized to the M-frame sync signal, which can either be externally provided or taken from the M-frame sync signal that is internally generated. Serial input data on TDAT[6]/TXDATI must contain bit positions for the overhead bits, although these are not used unless external insertion is enabled. The clock frequency is nominally 44.736 MHz and the transmit data input is sampled on the falling edge of the clock signal. The path delay of the transmitter from the serial data input to the positive and negative outputs is six cycles of the transmit clock. This delay includes B3ZS/HDB3 coding. The delay from the serial data input to the NRZ output is two clock cycles and the coding delay of the B3ZS encoder is four clock cycles.

#### 2.3 Transmitter Operation

If the TDAT[7]/TXSYI M-frame sync signal is provided, it is sampled on the rising edge of TXCKI and should have a low-to-high transition from the last bit of the M-frame (bit 680 of subframe 7) to the X1 bit (bit 1 of subframe 1). TXSYO is clocked out by the rising edge of TXCKI and may be used for synchronization of external circuitry. Serial data may alternatively be provided in response to the TXBCK/TXGAPCK pin without the need for providing frame synchronization or overhead bit slots. The gapped clock output is a gated version of TXCKI with one pulse gapped for each overhead bit position (one pulse every 85 clock cycles). A transmit overhead VALFCS/TXOVH bit position indicator pulse is available when the PPDL is not selected. This pulse is clocked out on the falling edge of TXCKI and may be of use for providing overhead bits externally. A timing diagram is presented in Figure 2-4 with propagation delays shown as negligible. Refer to the Electrical and Mechanical Specifications chapter for actual propagation delay specifications.

Figure 2-4. Transmitter Timing for Serial DS3 Mode

Figure 2-5 illustrates the transmitter timing for the parallel DS3 mode. This mode is enabled by setting the Parallel Data Enable bit [ParaEn;CR04.3] in the Feature Control Register and setting the Disable PPDL Transparency bit [DisPPDL;CR05.1] in the PPDL Control Register [CR05;0x05]. The SNDMSG pin should be tied high and the SNDFCS tied low to ensure that flags or FCS bytes are not transmitted.

2.3 Transmitter Operation

Figure 2-5. Transmitter Timing for Parallel DS3 Mode

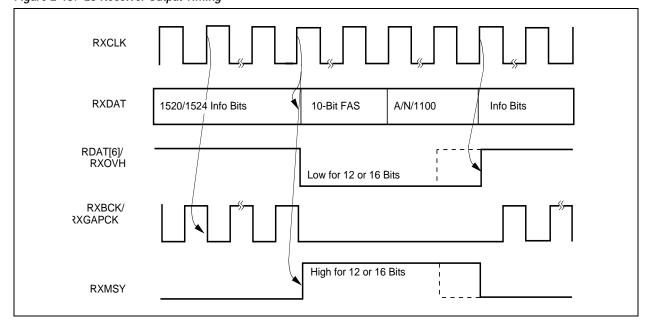

#### 2.3.3 E3 Mode

The clock and data edges for E3 mode have the same relationship as in DS3 mode. The synchronization overhead for E3 mode is 12 contiguous bits in each frame rather than being distributed throughout the frame. The input bits are synchronized to the M-frame sync signal, which can be externally provided or internally generated from the M-frame sync signal. Serial input data must contain bit positions for the overhead bits, although these are not used unless external insertion is enabled. The clock frequency is nominally 34.368 MHz and the transmit data input is sampled on the falling edge of the clock signal. The path delay of the transmitter from the serial data input to the positive and negative line driver outputs is seven cycles of the transmit clock. This delay includes HDB3 encoding. The delay from the serial data input to the NRZ output is two clock cycles and the coding delay of the HDB3 encoder is five clock cycles.

The TDAT[7]/TXSYI signal should have a low-to-high transition from the last bit of the M-frame (bit 1536) to the first bit of the FAS (bit 1). TXSYO may be used to synchronize external circuitry. Serial data may be provided alternatively in response to the TXBCK/TXGAPCK output without providing frame synchronization or overhead bit slots. Figure 2-6 illustrates the timing with propagation delays shown as negligible. Refer to the Electrical and Mechanical Specifications chapter for actual propagation delay specifications. Note that in E3 mode gapped clock TXBCK/TXGAPCK is one clock cycle late relative to the overhead bit positions when compared to the same relationship in DS3 mode. This clock can still be used for data input to the transmitter. The last data bit clocked in external circuitry by the gapped clock output should be held during the overhead interval and will be sampled by the first falling edge of TXCKI after the overhead interval. This bit will appear as the first bit in the information field after the overhead field.

#### 2.3 Transmitter Operation

Figure 2-6. Transmitter Timing for Serial E3 Mode

### 2.3.4 Framing Bit Generation

In DS3 mode, all F and M framing bits are automatically generated by the transmitter circuitry. Additionally, the transmitter calculates the parity of each M-frame and inserts this data into bits P1 and P2 of the following M-frame. Bits X1 and X2 contain ones unless the Transmit Alarm Control 0 bit [TxAlm0; CR00.4] in the Mode Control Register [CR00;0x00] is set. If set, bits X1 and X2 contain zeros. If C-bit parity mode is selected, all C-bit positions are generated automatically by the transmitter if the External C-Bit Insert bit [ExtCBit;CR00.2] is low. If high, all C-bits are generated internally except for the CP (subframe 3) an FEBE (subframe 4) bit positions. These bits must be provided on the CBITI pin at the proper time in response to TXCCK as shown in Figure 2-7. The CBITI data must be valid on the falling edge of TXCCK. This allows the chip to be used in a repeater mode with pass-through of the path parity and FEBE information. If C-bit parity mode is not selected, all C-bit positions come from either the serial data stream or the CBITI pin depending on the ExtCBit setting in the Mode Control Register. The X, P, M, and F bit positions may be inserted from the transmit serial data stream by setting External Overhead Insert bit [ExtOvh;CR00.3] high.

2.3 Transmitter Operation

In E3 mode, the FAS pattern is automatically generated by the transmitter circuitry. The transmitter also inserts the A-bit as determined from the Transmit Alarm Control 1 bit [TxAlm1;CR00.5] and the N-bit from the terminal data link circuitry. If ExtCBit is high, the N-bit must be provided on the CBITI pin in response to the rising edge of TXCCK. The TXOVH/VALFCS and TXSYO signals are active during the 12 bits of overhead. If the PPDL is enabled, the transmitter also inserts a 1100 pattern after the normal 12-bit framing sequence for a total of 16 overhead bits. This 16-bit pattern is for conformance with draft standard prETS 300 214 for SMDS applications. In this mode, the VALFCS/TXOVH and TXSYO signals are active during all 16 bits of overhead. All overhead bits can be inserted via the serial data input by setting the ExtOvh bit high.

Figure 2-7. C-Bit Input Timing

### 2.3.5 Alarm Signal Generation

Three alarm signals, yellow, AIS, and idle, can be generated by the transmitter in DS3 mode by setting the TxAlm[1,0] bit pair in the Mode Control Register.

The yellow alarm is contained in the X1 and X2 bits. The X1 and X2 bits are normally set to 1. The yellow alarm (X1 and X2 bits = 0) can be sent by setting the TxAlm bit pair to 01.

The AIS signal is enabled by setting the bit pair to 11. The AIS signal has valid framing and parity, all C-bits set to zero regardless of framing mode, both X-bits set to one, and the payload set to a 1010... pattern starting with 10 after each overhead bit.

The idle code signal is enabled by setting the bit pair to 10. The idle code signal has valid framing and parity, both X-bits set to one, and the payload set to a 1100... pattern starting with 11 after each overhead bit. If the framing mode is M13, all C-bits are set to zero during transmission of the idle signal. If the framing mode is C-bit parity, the C-bits in subframe 3 are set to zero, and the other C-bits are from the selected source. This allows full use of the terminal data link and transmit FEAC channel during transmission of idle code.

#### 2.3 Transmitter Operation

In C-bit parity mode with internal sourcing of the C-bits, FEBE alarms are generated automatically in the transmitter when the receiver detects either a frame bit error or a C-bit parity error in an M-frame. The 3-bit FEBE pattern that is transmitted is contained in the FEBE Pattern Bit Field [FEBEC[3:1];CR04.2:0] of the Feature Control Register. Bit 2 is placed in the C1 position of subframe 4 during the alarm condition, bit 1 is placed in the C2 position, and bit 0 is placed in the C3 position. When no alarm condition is present, the FEBE channel contains all ones. Therefore, to prevent disabling proper FEBE operation, the FEBE field should be written to any combination other than 111.

An unframed, all-ones signal can be transmitted by setting both TxAlm0 and TxAlm1 to a 1 and ExtOvh cleared to a 0.

In E3 mode, the AIS (unframed all-ones) is enabled by setting TxAlm0 high. The yellow alarm is enabled by setting TxAlm1 high. This causes the transmitted A-bit to be set to a one.

### 2.3.6 Terminal Data Link Transmitter

The terminal data link transmitter consists of the three C-bits in subframe 5 of the M-frame in DS3 mode or the N-bit in E3 mode and uses the LAPD protocol. When the Send Message bit [TxMsg;CR01.0] of the Terminal Data Link Control Register [CR01;0x01] is low, the data link transmitter is continuously sending idle flags (01111110). When high, message transmission is initiated. Transmission of the FCS bytes is controlled by the Send Frame Check Sequence bit [TxFCS;CR01.1]. If a nonstandard FCS is required, it may be loaded into the message buffer and transmitted as part of the message. A message in progress may be abandoned by setting the Abort Message bit [TxAbort;CR01.2]. This will cause an abort flag (11111110) to be transmitted, followed by idle flags, until the Send Message bit is reactivated. Two consecutive messages may share ending and beginning idle flags. The transmission bit [DisTxTDL;CR01.6] to a one. This causes all ones to be sent in the data link bit positions.

The terminal data link transmitter is under control of the C-Bit Parity Mode/Enable DLINT/SOURCELB (CBitP/DL;CR00.0), E3 Framing Mode [E3Frm;CR00.1], External C-Bit Insert, and Transmit Alarm Control bits in the Mode Control Register. In the Terminal Data Link Control Register, the transmitter is under the control of the TxMsg, TxFCS, TxAbort, Send Byte [TxByte[2:0];CR01.5:3], and DisTxTDL bits. An interrupt for use with data link operations is available on the DLINT/SOURCELB output pin and status bits for determining the interrupt source are located in the Data Link Interrupt Status Register [SR02;0x12].

The framer mode must be set to either C-bit parity mode or E3 mode for terminal data link transmission to take place. In C-bit parity mode, the three C-bits in subframe 5 of the M-frame will be used for transmission. In E3 mode, the N-bit will be used for transmission. When E3 mode is selected, the CBitP/DL bit must also be set to enable interrupts on the DLINT/SOURCELB pin. If neither mode is set, terminal data link transmission will not take place. If the ExtCBit bit is set in E3 mode, terminal data link transmission will be disabled. In C-bit parity mode, ExtCBit has no effect on terminal data link transmission. Setting the Transmit Alarm Control [1,0] bits for transmission of AIS or all ones in either C-bit parity mode or E3 mode will disable transmission of the terminal data link. Transmission of yellow alarms or idle codes has no effect on terminal data link transmission.

2.3 Transmitter Operation

If the framer is in a mode that allows data link transmission as described previously, then the Terminal Data Link Control Register is the main control register used for transmit data link operations. The DisTxTDL bit must be set low to enable operation of the data link. If high, an all-ones signal will be transmitted in the data link bit positions in the outgoing serial stream. With the data link enabled, the TxMsg, TxFCS, and TxAbort bits control operation. The TxByte[2:0] bits form a pointer to the Transmit Terminal Data Link Message Buffer [TxTdl;0x30–0x37] used by the data link transmitter.

The transmitter implements an LAPD data link per CCITT standard Q.921. The functions provided by the data link transmitter circuitry are transparency zero stuffing, FCS generation, idle flag generation, and abort flag generation. The total length of the message has no restrictions. Q.921 requires all messages be integral numbers of 8-bit bytes. The transmitter can only transmit 8-bit bytes. Byte transmission time for the transmitter is approximately 284 microseconds in C-bit parity mode and approximately 357 microseconds in E3 mode.

The Transmit Terminal Data Link Message Buffer is an 8-byte buffer provided for the transmit data link channel to minimize processor interruptions. Filling of this buffer is accomplished by the processor in the same manner as writes to control registers. This buffer can be read as well as written to verify contents. The buffer is divided into two halves to reduce the real-time requirements on the processor. The processor loads four bytes at a time, while the data link transmitter reads from the other half of the buffer. This gives the processor at least 1 msec to assemble the next four bytes of message for transmission before the next interrupt is issued. Interrupts are issued each time the transmitter circuitry reaches a 4-byte buffer boundary.

The transmitter must initialized with bits 0 through 6 of the Terminal Data Link Control Register written to zero. This will enable the transmitter to send idle flags on the data link. No interrupts are generated when the data link is sending idle flags, thus no processor intervention is required until a message is to be sent.

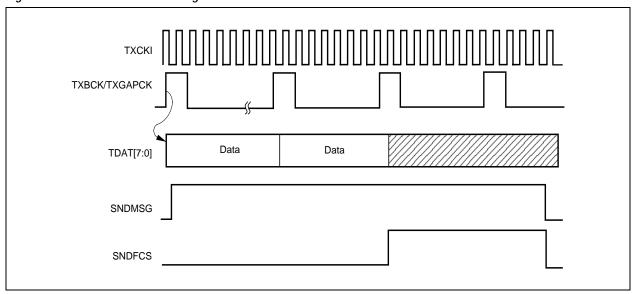

# 2.3.6.1 Sending a Message

Beginning with an idle channel, the processor writes the first four bytes of message data to the Transmit Terminal Data Link Message Buffer. The first byte of data to be transmitted should be written to address 0x30. The message is read from the buffer in ascending order starting at address 0x30 and ending at address 0x37. The Least Significant Bit (LSB) in each byte is the first transmitted. This buffer may be written well before the message is to be sent, if desired. After the first block of data is present in the buffer memory, the processor writes to the Terminal Data Link Control Register to begin transmission (TxMsg = 1, TxByte[2:0] = 011, TxFCS = 0, TxAbort = 0). The 3-bit TxByte[2:0] field is functionally split into two parts. The Most Significant Bit (MSB) indicates to the transmitter circuitry which half of the buffer to read from next. The two LSBs indicate the stop location, i.e., where the last message byte is located. When the new controls are latched by the transmitter circuitry, the processor will be interrupted for the next set of controls. Now, the processor has up to 1 msec to write a new set of controls to the control register. The processor may now also write the next block of data to the next half of the message buffer.

When the end of a message is reached, or in the event of a short message, there may not be exactly 4 bytes remaining. In this case, the processor writes the remaining data to the message buffer as usual. The processor now must write the highest location used to the TxByte[2:0] field. Also, the TxFCS bit is set to 1. This causes the FCS to be sent after this last block of data.

#### 2.3 Transmitter Operation