# L8560 Low-Power SLIC with Ringing

#### **Features**

- Full-feature set for central office applications

- Also ideal for ISDN terminal adapters, pair gain, and cable telephony applications

- Auxiliary input for second battery, and internal switch to enable its use to save power in short telephone loops

- 5 V only operation or optional ±5 V operation for reduced power consumption

- Low active power (85 mW typical) and scan power (61 mW typical) with 5 V only operation

- Low active power (68 mW typical with auxiliary battery) and scan power (45 mW typical) with ±5 V operation

- Quiet tip/ring polarity reversal

- Per-line ringing available for short loops

- Reduced overhead and increased current limit during ring mode for lower-battery operation or increased ring loop length

- Supports meter pulse injection

- Distortion-free full duplex from 0 mA dc loop current on-hook transmission

- Convenient operating states:

- Forward powerup

- Polarity reversal powerup

- Forward sleep

- Ground start

- Disconnect

- Adjustable supervision functions:

- Off-hook detector with longitudinal rejection

- Ground key detector with longitudinal rejection

- Ring trip detector

- Independent, adjustable dc and ac parameters:

- dc feed resistance (44-pin PLCC version)

- Loop current limit

- Termination impedance

- Thermal protection

### **Description**

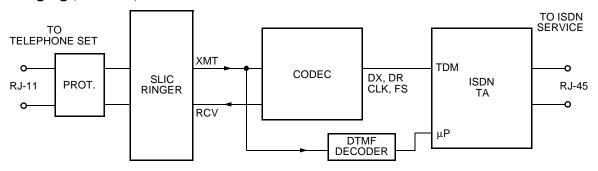

The L8560 full-feature, low-power subscriber line interface circuit (SLIC) is optimized for low power consumption while providing an extensive set of features. This part is ideal for ISDN terminal adapter applications and short-loop, power-sensitive applications such as pair gain and cable telephony. This part is also designed for PBX, DLC, or CO applications.

The SLIC includes an auxiliary battery input and a battery switch. In short-loop applications, SLICs can be used in high battery to present a high on-hook voltage, and then switched to low battery to reduce off-hook power.

To help minimize the required auxiliary battery voltage, the dc feed resistance and overhead voltage are set at 55  $\Omega$  and 6.7 V, respectively. This allows an undistorted on-hook transmission of a 3.14 dBm signal into a 900  $\Omega$  loop impedance.

The device offers the reverse battery function. Using the reverse battery, the device can provide a balanced power ring signal to tip and ring. In this mode of operation, the battery switch is used to apply a high-voltage battery during ringing and a lower-voltage battery during the talk and idle states. Also included in the L8560 is a dc current-limit switch, which increases the dc current limit during power ringing. In addition, dc overhead voltage is reduced during the ring state. With the battery and current-limit switches, and overhead reduction, the L8560 can provide sufficient power to ring a true North American 5 REN load of 1386  $\Omega$  + 40  $\mu F$ .

The device offers ring trip and loop closure supervision with 0.3 V and 2 mA hysteresis, respectively. It also includes the ground start state and ring ground detection. A summing node for meter pulse injection to 2.2 Vrms is also included. The 44-pin PLCC version also has a spare uncommitted op amp, which may be used for ac gain setting or meter pulse filtering.

# **Table of Contents**

| Contents                            | Page | Contents                                  | Page   |

|-------------------------------------|------|-------------------------------------------|--------|

| Features                            | 1    | Power Ringing Load                        | 28     |

| Description                         | 1    | Crest Factor                              |        |

| Pin Information                     | 6    | Current-Limit Switch                      | 29     |

| Functional Description              | 9    | Ring Trip                                 | 29     |

| Absolute Maximum Ratings            | 10   | Reference Designs for ISDN TA Application | ons 31 |

| Recommended Operating Conditions    | 11   | Design Considerations                     | 33     |

| Electrical Characteristics          |      | Unbalanced Bused Ring Signal Application  | n 33   |

| Ring Trip Requirements              | 16   | Ring Trip Detection                       | 33     |

| Test Configurations                 | 17   | ac Design                                 | 37     |

| Applications                        | 19   | First-Generation Codecs                   | 37     |

| Characteristic Curves               | 19   | Second-Generation Codecs                  | 37     |

| dc Applications                     | 21   | Third-Generation Codecs                   | 37     |

| Battery Feed                        | 21   | Design Examples                           | 39     |

| Overhead Voltage                    | 22   | Example 1, Real Termination               | 39     |

| Adjusting Overhead Voltage          | 23   | Example 2, Complex Termination            | 39     |

| Adjusting dc Feed Resistance        | 23   | Example 3, Complex Termination Without    |        |

| Adjusting Overhead Voltage and dc F |      | Spare Op Amp                              | 39     |

| Resistance Simultaneously           | 24   | Complex Termination Impedance Design      |        |

| Loop Range                          | 24   | Example Using L8560 Without Spare         |        |

| Off-Hook Detection                  | 24   | Op Amp                                    | 40     |

| Ring Ground Detection               | 25   | ac Interface Using First-Generation Codeo |        |

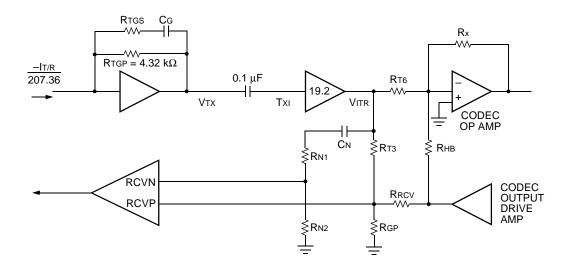

| Longitudinal Balance                | 25   | Transmit Gain                             | 41     |

| Power Derating                      |      | Receive Gain                              | 42     |

| Battery Switch                      | 26   | Hybrid Balance                            | 42     |

| Vcc/Vee Supplies                    | 27   | Blocking Capacitors                       | 43     |

| Power Ringing                       | 27   | Outline Diagrams                          | 44     |

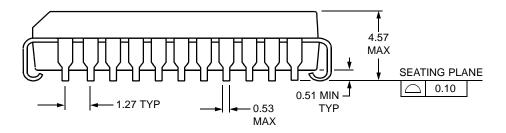

| Ringing SLIC Balanced Ring Signal   |      | 32-Pin PLCC                               | 44     |

| Generation                          | 27   | 44-Pin PLCC                               | 45     |

| POTS for ISDN Terminal Adapters     | 27   | Ordering Information                      | 46     |

# Table of Contents (continued)

| Figures                                         | Page           | Figure 32. Thevenin Equivalent Ring Trip Circuit    |     |

|-------------------------------------------------|----------------|-----------------------------------------------------|-----|

|                                                 |                | for Balanced Ringing SLIC                           | 29  |

| Figure 1. Functional Diagram                    |                | Figure 33. POTS Interface with Balanced Ringing     |     |

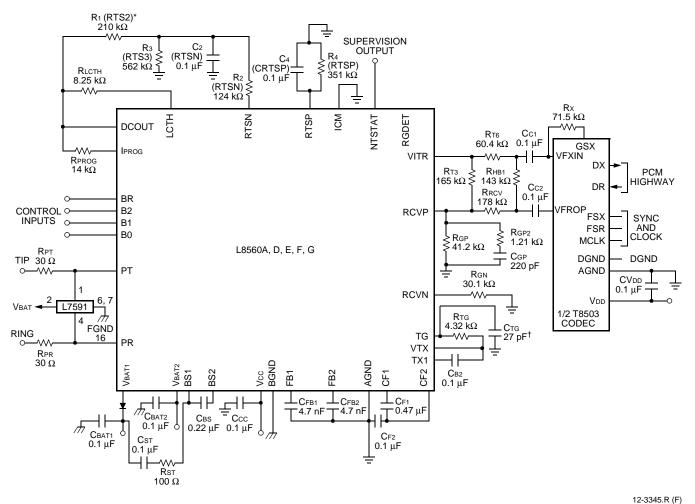

| Figure 2. 32-Pin Diagram (PLCC Chip)            | 6              | Using L8560 SLIC and T8503 Codec                    | 31  |

| Figure 3. 44-Pin Diagram (PLCC Chip)            |                | Figure 34. Ring Trip Equivalent Circuit and         |     |

| Figure 4. Ring Trip Circuits                    |                | Equivalent Application                              | 33  |

| Figure 5. Basic Test Circuit                    |                | Figure 35. Basic Loop Start Application Circuit     |     |

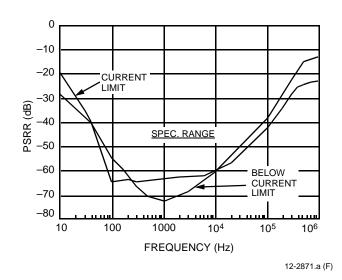

| Figure 6. Metallic PSRR                         |                | Using T7504 Codec and Bused                         |     |

| Figure 7. Longitudinal PSRR                     | 17             | Ringing                                             |     |

| Figure 8. Longitudinal Balance                  |                | Figure 36. Ground Start Application Circuit         | 35  |

| Figure 9. RFI Rejection                         |                | Figure 37. ac Equivalent Circuit Not Including      |     |

| Figure 10. Longitudinal Impedance               | 18             | Spare Op Amp                                        | 38  |

| Figure 11. ac Gains                             | 18             | Figure 38. ac Equivalent Circuit Including Spare    |     |

| Figure 12. L8560 Receive Gain and Hybrid        |                | Op Amp                                              | 38  |

| Balance vs. Frequency                           |                | Figure 39. Interface Circuit Using First-Generation |     |

| Figure 13. L8560 Transmit Gain and Return Lo    | )SS            | Codec (Blocking Capacitors Not                      |     |

| vs. Frequency                                   | 19             | Shown)                                              | 41  |

| Figure 14. L8560 Typical Vcc Power Supply       |                | Figure 40. ac Interface Using First-Generation      |     |

| Rejection                                       | 19             | Codec (Including Blocking Capacitors)               |     |

| Figure 15. L8560 Typical VBAT Power Supply      |                | for Complex Termination Impedance                   | 43  |

| Rejection                                       | 19             |                                                     |     |

| Figure 16. Loop Closure Program Resistor        |                |                                                     |     |

| Selection                                       |                | Tables Pa                                           | age |

| Figure 17. Ring Ground Detection Programmin     | ıg 20          |                                                     |     |

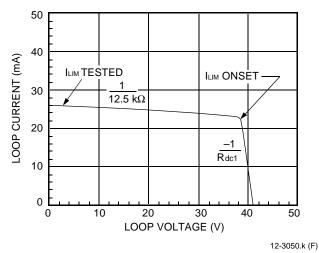

| Figure 18. Loop Current vs. Loop Voltage        | 20             | Table 1. L8560 Product Family Feature Summary       |     |

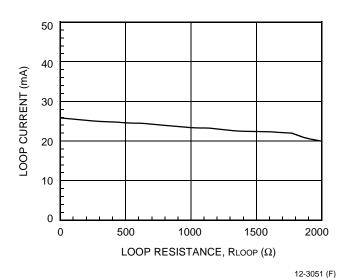

| Figure 19. Loop Current vs. Loop Resistance     |                | Table 2. Pin Descriptions                           |     |

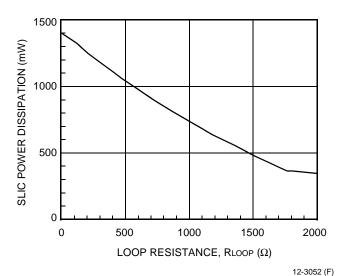

| Figure 20. L8560 Typical SLIC Power Dissipati   |                | Table 3. Input State Coding                         |     |

| vs. Loop Resistance                             |                | Table 4. Supervision Coding                         |     |

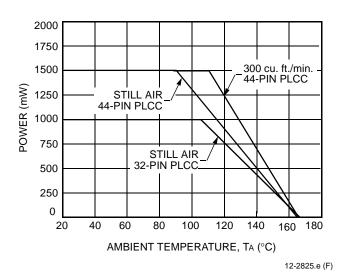

| Figure 21. Power Derating                       |                | Table 5. Power Supply                               |     |

| Figure 22. Loop Current vs. Loop Voltage        | 21             | Table 6. 2-Wire Port                                |     |

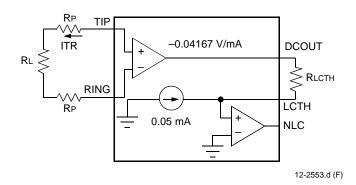

| Figure 23. SLIC 2-Wire Output Stage             | 23             | Table 7. Analog Pin Characteristics                 | 14  |

| Figure 24. Equivalent Circuit for Adjusting the |                | Table 8. Uncommitted Op Amp                         |     |

| Overhead Voltage                                | 23             | Characteristics (44-Pin PLCC Only)                  | 14  |

| Figure 25. Equivalent Circuit for Adjusting the |                | Table 9. ac Feed Characteristics                    |     |

| dc Feed Resistance                              | 23             | Table 10. Logic Inputs and Outputs                  | 16  |

| Figure 26. Adjusting Both Overhead Voltage as   |                | Table 11. Parts List for Balanced Ringing Using     |     |

| dc Feed Resistance                              | 24             | T8503 Codec                                         | 32  |

| Figure 27. Off-Hook Detection Circuit           | 24             | Table 12. Parts List for Loop Start with Bused      |     |

| Figure 28. POTS Controlled from an ISDN         |                | Ringing and Ground Start Applications.              |     |

| Terminal Adapter                                | 28             | Table 13. 600 $\Omega$ Design Parameters            | 37  |

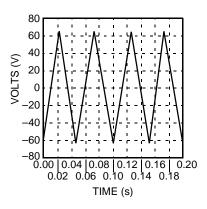

| Figure 29. Ringing Waveform Crest Factor = 1.   |                |                                                     |     |

|                                                 | .6 28          |                                                     |     |

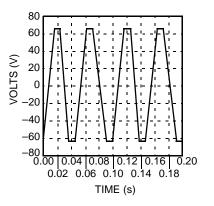

| Figure 30. Ringing Waveform Crest Factor = 1.   | .6 28          |                                                     |     |

|                                                 | .6 28<br>.2 28 |                                                     |     |

#### **Description** (continued)

The L8560 product family is graded by different features, specifications, and package options. The L8560Axx is the basic full-feature SLIC that operates with 5 V and a battery supply, and is available in the 32-pin PLCC (AAU) package and the 44-pin PLCC package (AP). This part is graded as the 54 dB longitudinal balance part. Additional features (spare op amp and overhead voltage programming) are available in the 44-pin PLCC package.

The L8560CAU is available only in the 32-pin PLCC package and has a feature set similar to the AAU version, except the CAU version requires +5 V, -5 V, and battery power supplies. With this option, power consumption is greatly reduced.

The L8560DAU and L8560EP are available in the 32-pin and 44-pin PLCC packages and have feature sets identical to the L8560AAU and L8560AP, respectively, with the following modifications. These parts are graded as high longitudinal balance (63 dB), and have an additional logic state (scan with low battery) which allows for low on-hook power dissipation.

The L8560FAU and L8560GP are available in the 32-pin and 44-pin PLCC packages and have feature sets identical to the L8560AAU and L8560AP, respectively, with the following modifications. These parts are graded for lower longitudinal balance (50 dB), and have an additional logic state (scan with battery) which allows for low on-hook power dissipation.

Table 1 below summarizes the features in the L8560 product family.

**Table 1. L8560 Product Family Feature Summary**

| Factions                                   | L8560 |     |     |     |     |     |     |  |

|--------------------------------------------|-------|-----|-----|-----|-----|-----|-----|--|

| Feature                                    | AAU   | AP  | CAU | DAU | EP  | FAU | GP  |  |

| 32-Pin PLCC                                | Х     | NA  | Х   | Х   | NA  | Х   | NA  |  |

| 44-Pin PLCC                                | NA    | Х   | NA  | NA  | Х   | NA  | Χ   |  |

| 5 V Operation                              | Х     | Х   | NA  | X   | Х   | Х   | Х   |  |

| ±5 V Operation (reduced power consumption) | NA    | NA  | Х   | NA  | NA  | NA  | NA  |  |

| Operational VBAT1 (V)                      | -70   | -70 | -70 | -70 | -70 | -70 | -70 |  |

| Battery Switch                             | Х     | Х   | Х   | X   | Х   | Х   | Х   |  |

| Balanced Ring Mode                         | Х     | Х   | Х   | X   | Х   | Х   | Х   |  |

| Adjustable Overhead                        | NA    | Х   | NA  | NA  | Χ   | NA  | Χ   |  |

| Spare Op Amp                               | NA    | Х   | NA  | NA  | Х   | NA  | Х   |  |

| Reverse Battery                            | Х     | Х   | Х   | Х   | Х   | Х   | Х   |  |

| Scan Mode                                  | Х     | Х   | Х   | X   | Х   | Х   | Х   |  |

| Scan Mode with Low Battery                 | NA    | NA  | NA  | X   | Х   | Х   | Х   |  |

| Longitudinal Balance (dB)*                 | 54    | 54  | 54  | 63  | 63  | 50  | 50  |  |

| On-hook Transmission                       | Х     | Х   | Х   | X   | Х   | Х   | Х   |  |

| Ground Start                               | Х     | Х   | Х   | X   | Х   | Х   | Х   |  |

| Loop Start                                 | Х     | Х   | Х   | Χ   | Х   | Х   | Х   |  |

| Ring Trip Detector                         | Х     | Х   | Х   | Χ   | Х   | Х   | Х   |  |

| Programmable Current Limit                 | Х     | Х   | Х   | Χ   | Х   | Х   | Х   |  |

| Thermal Protection                         | Х     | Х   | Х   | X   | Χ   | Х   | Χ   |  |

<sup>\*</sup> More information is provided in the Applications section of this document.

# **Description** (continued)

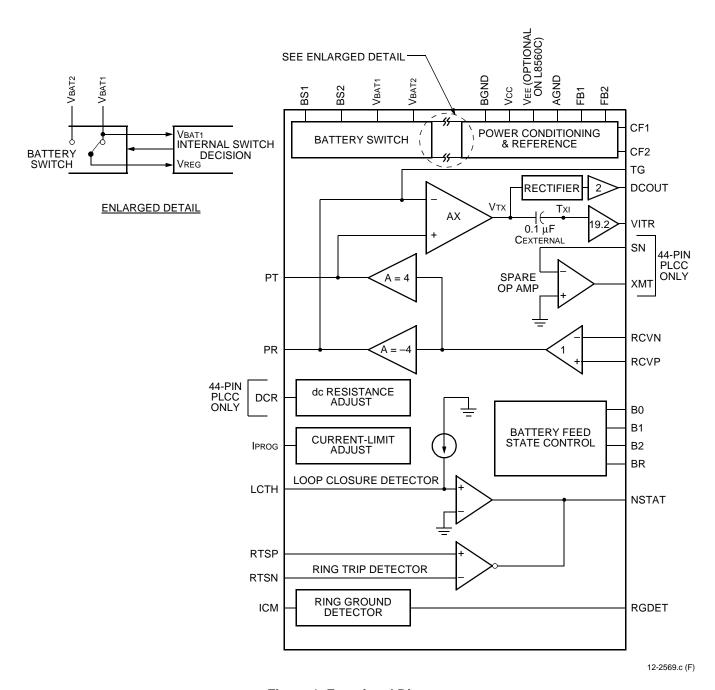

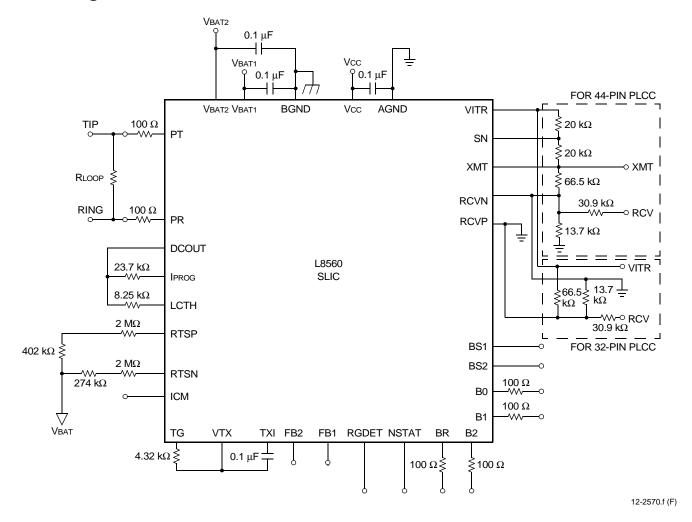

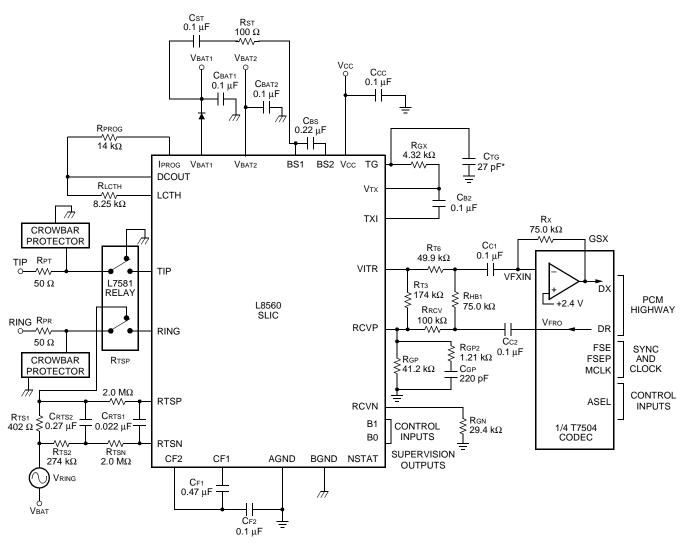

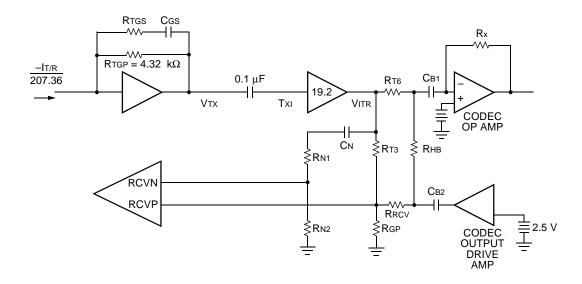

Figure 1. Functional Diagram

### **Pin Information**

12-2548.L (F)

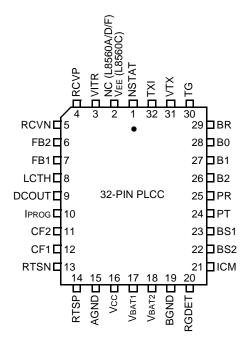

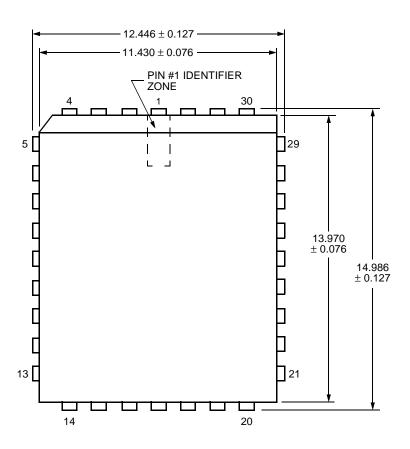

Figure 2. 32-Pin Diagram (PLCC Chip)

12-2548.f (F)

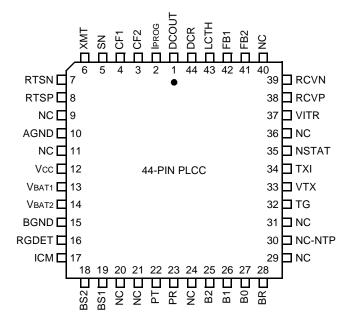

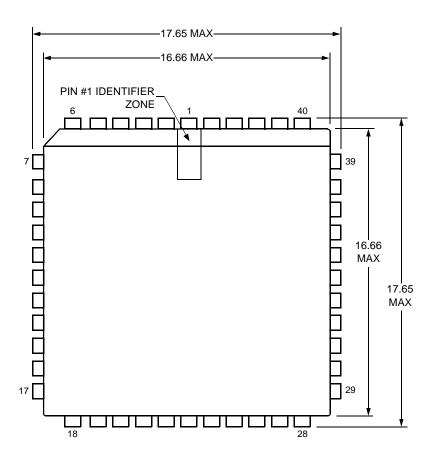

Figure 3. 44-Pin Diagram (PLCC Chip)

# Pin Information (continued)

**Table 2. Pin Descriptions**

| 32-Pin | 44-Pin | Symbol | Туре | Description                                                                                                                                                                                               |  |  |

|--------|--------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 9      | 1      | DCOUT  | 0    | <b>dc Output Voltage.</b> This output is a voltage that is directly proportional to the absolute value of the differential tip/ring current.                                                              |  |  |

| 10     | 2      | IPROG  | l    | <b>Current-Limit Program Input.</b> A resistor to DCOUT sets the dc current limit of the device.                                                                                                          |  |  |

| 11     | 3      | CF2    | _    | Filter Capacitor 2. Connect a 0.1 μF capacitor from this pin to AGND.                                                                                                                                     |  |  |

| 12     | 4      | CF1    | _    | Filter Capacitor 1. Connect a 0.47 μF capacitor from this pin to pin CF2.                                                                                                                                 |  |  |

| _      | 5      | SN     | l    | <b>Summing Node.</b> The inverting input of the uncommitted operational amplifier. A resistor or network to XMT sets the gain (44-pin PLCC only).                                                         |  |  |

| _      | 6      | XMT    | 0    | <b>Transmit ac Output Voltage.</b> The output of the uncommitted operational amplifier (44-pin PLCC only).                                                                                                |  |  |

| 13     | 7      | RTSN   | l    | <b>Ring Trip Sense Negative.</b> Connect this pin to the ringing generator signal through a high-value resistor.                                                                                          |  |  |

| 14     | 8      | RTSP   | I    | <b>Ring Trip Sense Positive.</b> Connect this pin to the ring relay and the ringer series resistor through a high-value resistor.                                                                         |  |  |

| _      | 9      | NC     | _    | No Connection. May be used as a tie point.                                                                                                                                                                |  |  |

| 15     | 10     | AGND   |      | Analog Signal Ground.                                                                                                                                                                                     |  |  |

| _      | 11     | NC     | _    | No Connection. May be used as a tie point.                                                                                                                                                                |  |  |

| 16     | 12     | Vcc    |      | 5 V Power Supply.                                                                                                                                                                                         |  |  |

| 17     | 13     | VBAT1  |      | Battery Supply. Negative high-voltage battery, higher in magnitude than VBAT2.                                                                                                                            |  |  |

| 18     | 14     | VBAT2  |      | <b>Auxiliary Battery Supply.</b> Negative high-voltage battery, lower in magnitude than VBAT1, used to reduce power dissipation on short loops.                                                           |  |  |

| 19     | 15     | BGND   | _    | Battery Ground. Ground return for the battery supply.                                                                                                                                                     |  |  |

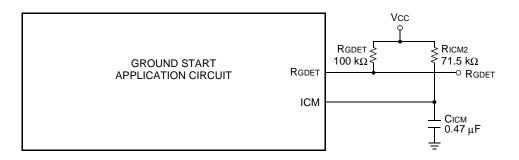

| 20     | 16     | RGDET  | 0    | <b>Ring Ground Detect.</b> When high, this open-collector output indicates the presence of a ring ground. To use, connect a 100 k $\Omega$ resistor to Vcc.                                               |  |  |

| 21     | 17     | ICM    | I    | <b>Common-Mode Current Sense.</b> To program ring ground sense threshold, connect a resistor to Vcc and connect a capacitor to AGND to filter 50/60 Hz. If unused, the pin should be connected to ground. |  |  |

| 22     | 18     | BS2    | 1    | <b>Battery Switch Slowdown.</b> Connect a 0.22 μF capacitor to pin BS1.                                                                                                                                   |  |  |

| 23     | 19     | BS1    |      | Battery Switch Slowdown. Connect a 0.22 $\mu F$ capacitor to pin BS2. Also, connect a 0.1 $\mu F$ capacitor in series with a 100 $\Omega$ resistor from BS1 to V <sub>BAT1</sub> for stability.           |  |  |

|        | 20     | NC     |      | No Connection. May be used as a tie point.                                                                                                                                                                |  |  |

|        | 21     | NC     | _    | No Connection. May be used as a tie point.                                                                                                                                                                |  |  |

| 24     | 22     | PT     | I/O  | <b>Protected Tip.</b> The output of the tip driver amplifier and input to loop sensing. Connect to loop through overvoltage protection.                                                                   |  |  |

| 25     | 23     | PR     | I/O  | <b>Protected Ring.</b> The output of the ring driver amplifier and input to loop sensing circuitry. Connect to loop through overvoltage protection.                                                       |  |  |

# Pin Information (continued)

Table 2. Pin Descriptions (continued)

| 32-Pin | 44-Pin | Symbol | Type | Description                                                                                                                                                                                                                                                                                         |  |  |  |

|--------|--------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| _      | 24     | NC     |      | No Connection. May be used as a tie point.                                                                                                                                                                                                                                                          |  |  |  |

| 26     | 25     | B2     | I    | State Control Input. B0, B1, B2, and BR determine the state of the SLIC. See Table 3. Pin B2 has a 40 $\rm k\Omega$ pull-up.                                                                                                                                                                        |  |  |  |

| 27     | 26     | B1     |      | State Control Input. B0, B1, B2, and BR determine the state of the SLIC. See Table 3. Pin B1 has a 40 $\rm k\Omega$ pull-up.                                                                                                                                                                        |  |  |  |

| 28     | 27     | В0     | I    | State Control Input. B0, B1, B2, and BR determine the state of the SLIC. See Table 3. Pin B0 has a 40 ${\rm k}\Omega$ pull-up.                                                                                                                                                                      |  |  |  |

| 29     | 28     | BR     | Ι    | State Control Input. B0, B1, B2, and BR determine the state of the SLIC. See Table 3. Pin BR has a 40 k $\Omega$ pull-up.                                                                                                                                                                           |  |  |  |

| _      | 29     | NC     | _    | No Connection. May be used as a tie point.                                                                                                                                                                                                                                                          |  |  |  |

| _      | 30     | NC-NTP | _    | No Connection. May not be used as a tie point.                                                                                                                                                                                                                                                      |  |  |  |

| _      | 31     | NC     | _    | No Connection. May be used as a tie point.                                                                                                                                                                                                                                                          |  |  |  |

| 30     | 32     | TG     | _    | Transmit Gain. Connect a 4.32 kΩ resistor from this pin to VTX.                                                                                                                                                                                                                                     |  |  |  |

| 31     | 33     | VTX    | 0    | The voltage at this pin is directly proportional to the differential tip/ring current.                                                                                                                                                                                                              |  |  |  |

| 32     | 34     | TXI    |      | ac/dc Separation. Connect a 0.1 μF capacitor from this pin to VTX.                                                                                                                                                                                                                                  |  |  |  |

| 1      | 35     | NSTAT  | 0    | Loop Detector Output/Ring Trip Detector Output. This output is a wired-OR of the NLC/NRDET outputs. When low, this logic output indicates that an off-hook condition exists or that ringing has been tripped.                                                                                       |  |  |  |

| 2      | _      | VEE    | -    | -5 V Power Supply L8560C.                                                                                                                                                                                                                                                                           |  |  |  |

| 2      | _      | NC     | _    | No Connection L8560A/D/F. May be used as a tie point.                                                                                                                                                                                                                                               |  |  |  |

| _      | 36     | NC     | _    | No Connection. May be used as a tie point.                                                                                                                                                                                                                                                          |  |  |  |

| 3      | 37     | VITR   | 0    | <b>ac Output Voltage.</b> This output is a voltage that is directly proportional to the differential ac tip/ring current.                                                                                                                                                                           |  |  |  |

| 4      | 38     | RCVP   | I    | Receive ac Signal Input (Noninverting). This high-impedance input controls the ac differential voltage on tip and ring.                                                                                                                                                                             |  |  |  |

| 5      | 39     | RCVN   | Ι    | <b>Receive ac Signal Input (Inverting).</b> This high-impedance input controls the ac differential voltage on tip and ring.                                                                                                                                                                         |  |  |  |

| _      | 40     | NC     | -    | No Connection. May be used as a tie point.                                                                                                                                                                                                                                                          |  |  |  |

| 6      | 41     | FB2    | -    | Polarity Reversal Slowdown. Connect a capacitor to ground.                                                                                                                                                                                                                                          |  |  |  |

| 7      | 42     | FB1    |      | Polarity Reversal Slowdown. Connect a capacitor to ground.                                                                                                                                                                                                                                          |  |  |  |

| 8      | 43     | LCTH   | I    | <b>Loop Closure Threshold Input.</b> Connect a resistor to DCOUT to set off-hook threshold.                                                                                                                                                                                                         |  |  |  |

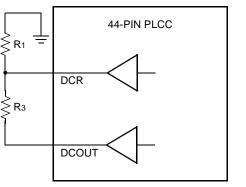

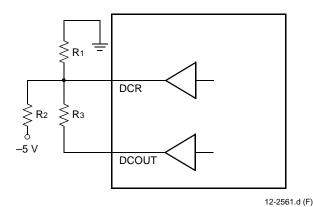

| _      | 44     | DCR    | I    | dc Resistance. Short to analog ground for dc feed resistance of 55 $\Omega$ . The dc feed resistance can be increased to a nominal 760 $\Omega$ by shorting DCR to DCOUT. Intermediate values can be set by a simple resistor divider from DCOUT to ground with the trip at DCR (44-pin PLCC only). |  |  |  |

# **Functional Description**

**Table 3. Input State Coding**

| В0 | B1  | B2 | BR | State/Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|-----|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 1   | 0  | 1  | <b>Powerup, Forward Battery VBAT2.</b> Pin PT is positive with respect to pin PR. VBAT2 is applied to the tip/ring drive amplifiers. On-hook transmission capability. All supervision active—an off-hook condition or a ring trip causes output NSTAT to go low.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1  | 0   | 0  | 1  | <b>Powerup, Reverse Battery VBAT2.</b> Pin PR is positive with respect to pin PT. VBAT2 is applied to the tip/ring drive amplifiers. On-hook transmission capability. All supervision active—an off-hook condition or a ring trip causes output NSTAT to go low.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1  | 1   | 1  | 1  | <b>Powerup, Forward Battery VBAT1.</b> Pin PT is positive with respect to pin PR. VBAT1 is applied to the tip/ring drive amplifiers. On-hook transmission capability. All supervision active—an off-hook condition or a ring trip causes output NSTAT to go low.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1  | 0   | 1  | 1  | <b>Powerup, Reverse Battery VBAT1.</b> Pin PR is positive with respect to pin PT. VBAT1 is applied to the tip/ring drive amplifiers. On-hook transmission capability. All supervision active—an off-hook condition or a ring trip causes output NSTAT to go low.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0  | 1   | 1  | 1  | <b>Ground Start.</b> Tip drive amplifier is turned off. The device presents a high impedance (>100 k $\Omega$ ) to pin PT and a current-limited battery (VBAT1) to pin PR. Output pin RGDET indicates current flowing in the ring lead.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0  | 0   | 1  | 1  | <b>Low-Power Scan.</b> Except for off-hook supervision, all circuits are shut down to conserve power. Only the off-hook detector affects output pin NSTAT. VBAT1 is applied to the tip/ring drive amplifiers. Pin PT is positive with respect to pin PR. On-hook transmission is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0  | 1   | 0  | 1  | <b>Low-Power Scan (L8560D/E/F/G Only).</b> Except for off-hook supervision, all circuits are shut down to conserve power. Only the off-hook detector affects output pin NSTAT. VBAT2 is applied to the tip/ring drive amplifiers. Pin PT is positive with respect to pin PR. On-hook transmission is disabled.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0  | 0   | 0  | 1  | <b>Forward Disconnect.</b> The tip and ring amplifiers are turned off and the SLIC goes into a high-impedance state (>100 k $\Omega$ ). V <sub>BAT2</sub> is applied to the SLIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1  | 1/0 | 1  | 0  | <b>Ring State.</b> SLIC is powered up. V <sub>BAT1</sub> is applied to the tip and ring amplifiers. Current limit is increased by a factor of 2.8. Overhead voltage is reduced to approximately 2.4 V. These conditions are necessary to supply sufficient power to drive a true North American 5 REN ringing load (1386 $\Omega$ + 40 $\mu$ F). Loop closure detector is disabled—only the ring trip detector affects output pin NSTAT. To apply a balanced ring signal to pins PR and PT, apply a 0 V to 5 V square wave to input pin B1. Ringing frequency is the frequency of the input wave at B1. To shape the ring signal at pins PR and PT, connect a capacitor from pin FB1 to ground and from pin FB2 to ground. |

**Table 4. Supervision Coding**

| Pin NSTAT                    | Pin RGDET          |

|------------------------------|--------------------|

| 0 = off-hook or ring trip    | 1 = ring ground    |

| 1 = on-hook and no ring trip | 0 = no ring ground |

## **Absolute Maximum Ratings** (TA = 25 °C)

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                                  | Symbol       | Value               | Unit |

|--------------------------------------------|--------------|---------------------|------|

| 5 V Power Supply                           | Vcc          | 7.0                 | V    |

| −5 V Power Supply (L8560C)                 | VEE          | -7.0                | V    |

| Battery (talking) Supplies                 | VBAT1, VBAT2 | <del>-</del> 75     | V    |

| VBAT2 Magnitude                            | IVBAT2I      | IVBAT1I + 0.4       | V    |

| Logic Input Voltage                        | _            | -0.5 to +7.0        | V    |

| Analog Input Voltage                       | _            | -7.0 to +7.0        | V    |

| Maximum Junction Temperature               | TJ           | 165                 | °C   |

| Storage Temperature Range                  | Tstg         | -40 to +125         | °C   |

| Relative Humidity Range                    | Rн           | 5 to 95             | %    |

| Ground Potential Difference (BGND to AGND) | _            | ±3                  | V    |

| PT or PR Fault Voltage (dc)                | Vpt, Vpr     | (VBAT1 – 5) to +3   | V    |

| PT or PR Fault Voltage (10 x 1000 μs)      | Vpt, Vpr     | (VBAT1 – 15) to +15 | V    |

| Current into Ring Trip Inputs              | IRTSP, IRTSN | ±240                | μΑ   |

Note: The IC can be damaged unless all ground connections are applied before, and removed after, all other connections. Furthermore, when powering the device, the user must guarantee that no external potential creates a voltage on any pin of the device that exceeds the device ratings. Some of the known examples of conditions that cause such potentials during powerup are 1) an inductor connected to tip and ring can force an overvoltage on VBAT through the protection devices if the VBAT connection chatters, and 2) inductance in the VBAT lead could resonate with the VBAT filter capacitor to cause a destructive overvoltage.

### **Recommended Operating Conditions**

| Parameter                                                         | Min        | Тур  | Max             | Unit |

|-------------------------------------------------------------------|------------|------|-----------------|------|

| Ambient Temperature                                               | -40        | _    | 85              | °C   |

| Loop Closure Threshold-detection Programming Range                | 5          | 10   | ILIM            | mA   |

| dc Loop Current-limit Programming Range                           | 5          | 40   | 50              | mA   |

| On- and Off-hook 2-wire Signal Level (@ $Z$ LOOP = 200 $\Omega$ ) | _          | _    | 2.2             | Vrms |

| ac Termination Impedance Programming Range                        | 150        | 600  | 1300            | Ω    |

| VBAT1                                                             | -24        | -48  | <del>-7</del> 0 | V    |

| VBAT2                                                             | <b>–16</b> | _    | VBAT1           | V    |

| Vcc                                                               | 4.5        | 5.0  | 5.5             | V    |

| VEE (L8560C)                                                      | -4.75      | -5.0 | <b>−</b> 5.5    | V    |

| dc Feed Resistance Programming Range (excl. RP)                   | 55         | 55   | 760             | Ω    |

### **Electrical Characteristics**

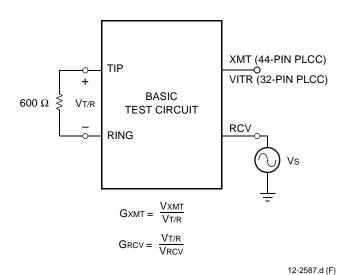

Minimum and maximum values are testing requirements in the temperature range of 25 °C to 85 °C and battery range of –24 V to –70 V. These minimum and maximum values are guaranteed to –40 °C based on component simulations and design verification of samples, but devices are not tested to –40 °C in production. The test circuit shown in Figure 5 is used, unless otherwise noted. Positive currents flow into the device.

Typical values are characteristics of the device design at 25 °C based on engineering evaluations and are not part of the test requirements. Supply values used for typical characterization are Vcc = 5.0 V, VEE = -5.0 V, VBAT1 = -48 V, VBAT2 = -25.5 V, unless otherwise noted.

**Table 5. Power Supply**

Vcc = 5.0 V, Vee = -5.0 V, Vec = -48 V, Vec = -19 V, unless otherwise noted.

| Parameter                                                             | Min | Тур         | Max        | Unit     |

|-----------------------------------------------------------------------|-----|-------------|------------|----------|

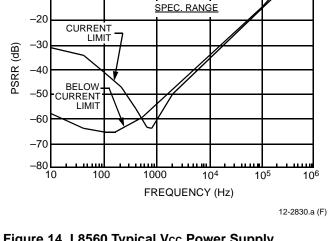

| Power Supply Rejection 500 Hz to 3 kHz                                |     | _           |            |          |

| (See Figures 6, 7, 14, and 15.) <sup>1</sup> :                        |     |             |            |          |

| Vcc (1 kHz), Vee (1 kHz) <sup>2</sup>                                 | 35  | _           | _          | dB       |

| VBAT1, VBAT2 (500 Hz—3 kHz)                                           | 45  | _           | _          | dB       |

| Thermal Protection Shutdown (T <sub>jc</sub> )                        |     | 165         | _          | °C       |

| Thermal Resistance, Junction to Ambient (θJA), Still Air, 44-pin PLCC | _   | 47          | _          | °C/W     |

| Thermal Resistance, Junction to Ambient (θJA), Still Air, 32-pin PLCC | _   | 60          |            | °C/W     |

| Power Supply—Powerup, No Loop Current, VBAT2 Applied                  |     |             |            |          |

| L8560A/D/E/F/G:                                                       |     |             |            | .        |

| lcc                                                                   | _   | 6.0         | 7.2        | mA       |

| IBAT1                                                                 |     | 120         | 200        | μA       |

| IBAT2                                                                 | _   | 2.6         | 3.2        | mA       |

| Power Supply—Powerup, No Loop Current, VBAT1 Applied:                 |     | 0.0         | 7.0        |          |

| Icc (L8560A/D/E/F/G)                                                  |     | 6.0         | 7.2        | mA       |

| IBAT1 (L8560A)                                                        | _   | 2.8         | 3.3<br>2.0 | mA<br>mA |

| Іват1 (L8560D/E/F/G)<br>Іват2 (L8560D/E/F/G)                          | _   | 1.65<br>1.0 | 1.3        | mA       |

| ,                                                                     |     | 1.0         | 1.3        | IIIA     |

| Power Supply—Scan Mode, Forward Battery, No Loop Current,             |     |             |            |          |

| VBAT1 Applied:<br>Icc (L8560A/D/E/F/G)                                |     | 4.0         | 5.2        | mA       |

| IBAT1 (L8560A)                                                        | _   | 1.3         | 1.6        | mA       |

| IBAT1 (L8560D/E/F/G)                                                  | _   | 0.5         | 0.75       | mA       |

| IBAT2 (L8560D/E/F/G)                                                  | _   | 0.9         | 1.2        | mA       |

| Power Supply—Scan Mode, Forward Battery, No Loop Current,             |     |             |            |          |

| VBAT2 Applied:                                                        |     |             |            |          |

| Icc                                                                   |     | 4.1         | _          | mA       |

| IBAT1 (VBAT1 = -65 V)                                                 | _   | 200         |            | μA       |

| $I_{BAT2} (V_{BAT2} = -30 \text{ V})$                                 | _   | 1.2         |            | mA       |

| Power Supply—Powerup, No Loop Current, L8560C Only:                   |     |             |            |          |

| lcc                                                                   | _   | 5.8         | 7.2        | mA       |

| lee                                                                   |     | 0.9         | 1.26       | mA       |

| Іватı (Vватı applied)                                                 | _   | 1.65        | 2.2        | mA       |

| Іват2 (Vват2 applied)                                                 |     | 1.50        | 1.96       | mA       |

| IBAT1 (VBAT2 applied)                                                 |     | 120         | 200        | μΑ       |

| Power Supply—Scan, Forward Battery, No Loop Current, VBAT1            |     |             |            |          |

| Applied, L8560C Only:                                                 |     |             |            |          |

| lcc                                                                   | _   | 4.1         | 5.5        | mA       |

| lee                                                                   |     | 0.81        | 1.1        | mA       |

| Іват (Vват1 applied)                                                  | _   | 0.43        | 0.56       | mA       |

| Power Supply—Ring Mode, No Loop Current:                              |     |             |            |          |

| lcc                                                                   | _   | 6.45        | _          | mA       |

| IBAT1                                                                 | _   | 2.2         | _          | mA       |

<sup>1.</sup> This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>2.</sup> VEE used for L8560C version only.

Table 6. 2-Wire Port

| Parameter                                                                                                                                                                                                                                                                                                                                                                                            | Min                                           | Тур                                           | Max                                | Unit                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|------------------------------------|---------------------------------------|

| Tip or Ring Drive Current = dc + Longitudinal + Signal Currents                                                                                                                                                                                                                                                                                                                                      | 65                                            | _                                             | _                                  | mA                                    |

| Signal Current                                                                                                                                                                                                                                                                                                                                                                                       | 15                                            | _                                             | _                                  | mArms                                 |

| Longitudinal Current Capability per Wire <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                | 8.5                                           | 15                                            | _                                  | mArms                                 |

| dc Loop Current Limit <sup>2</sup> :<br>Programmability Range <sup>3</sup><br>Accuracy (B0 = BR = 5 V, RLOOP = 100 $\Omega$ , VBAT1 = -48 V<br>or VBAT2 = -25.5 V active)                                                                                                                                                                                                                            | 5<br>—                                        |                                               | 50<br>±5                           | mA<br>%                               |

| Powerup Open Loop Voltage Levels: Differential Voltage – VBAT2 (VBAT2 = -25.5 V) Differential Voltage – VBAT1 (VBAT1 = -48 V) <sup>4</sup> Differential Voltage – VBAT1 (ring mode)                                                                                                                                                                                                                  | VBAT2 + 6.9 <br> VBAT1 + 7.1 <br> VBAT1 + 5.5 | VBAT2 + 6.5 <br> VBAT1 + 6.7 <br> VBAT1 + 2.4 | VBAT2 + 6.1 <br> VBAT1 + 6.3 <br>— | > > >                                 |

| Ground Start State: PT Resistance                                                                                                                                                                                                                                                                                                                                                                    | 100                                           | _                                             | _                                  | kΩ                                    |

| dc Feed Resistance (for ILOOP below current limit)                                                                                                                                                                                                                                                                                                                                                   | _                                             | 55                                            | 80                                 | Ω                                     |

| Loop Resistance Range (3.17 dBm overload into 600 $\Omega$ ; not including protection):<br>ILOOP = 20 mA at VBAT1 = -48 V<br>ILOOP = 20 mA at VBAT2 = -24 V                                                                                                                                                                                                                                          | 1940<br>760                                   | _<br>_                                        | _<br>_<br>_                        | $\Omega \ \Omega$                     |

| Longitudinal to Metallic Balance—IEEE <sup>5</sup> Std. 455 (See Figure 8.) <sup>6, 7</sup> : L8560A/C: 200 Hz to 2999 Hz Forward/Reverse Battery 3000 Hz to 3400 Hz Forward/Reverse Battery L8560D/E: 200 Hz to 2999 Hz Forward Battery 3000 Hz to 3400 Hz Forward Battery 200 Hz to 2999 Hz Reverse Battery 3000 Hz to 3400 Hz Reverse Battery L8560F/G: 200 Hz to 2999 Hz Forward/Reverse Battery | 54<br>49<br>63<br>58<br>58<br>54              | 59<br>54<br>68<br>63<br>63<br>59              | -<br>-<br>-<br>-<br>-              | 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 |

| 3000 Hz to 3400 Hz Forward/Reverse Battery                                                                                                                                                                                                                                                                                                                                                           | 45                                            | 50                                            | _                                  | dB                                    |

| Metallic to Longitudinal Balance: 200 Hz to 4 kHz                                                                                                                                                                                                                                                                                                                                                    | 46                                            | _                                             | _                                  | dB                                    |

| RFI Rejection (See Figure 9.) <sup>3</sup> :<br>0.5 Vrms, 50 Ω Source, 30% AM Mod. 1 kHz<br>500 kHz to 100 MHz                                                                                                                                                                                                                                                                                       | _                                             | <b>–</b> 55                                   | <b>-45</b>                         | dBV                                   |

<sup>1.</sup> The longitudinal current is independent of dc loop current.

<sup>2.</sup> Current-limit ILIM is programmed by a resistor, RPROG, from pin IPROG to DCOUT. ILIM is specified at the loop resistance where current limiting begins (see Figure 22). Select RPROG ( $k\Omega$ ) = 0.616 x ILIM (mA) – onset of current limit with input BR high. When input BR is low, the current will be increased by a factor of 2.8.

<sup>3.</sup> This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>4.</sup> Specification is reduced to |VBAT1 + 10.5 V| minimum when VBAT1 = -70 V at 85 °C. 5. *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

<sup>6.</sup> Longitudinal balance of circuit card will depend on loop series protection resistor matching and magnitude.

<sup>7.</sup> Tested at 1000 Hz only. Full frequency specifications guaranteed by design and device characterization.

**Table 7. Analog Pin Characteristics**

| Parameter                                                       | Min      | Тур               | Max          | Unit |

|-----------------------------------------------------------------|----------|-------------------|--------------|------|

| Differential PT/PR Current Sense (DCOUT):                       |          |                   |              |      |

| Gain (PT/PR to DCOUT)                                           | _        | <del>-4</del> 1.7 | _            | V/A  |

| Offset Voltage @ ILOOP = 0                                      | -200     |                   | 200          | mV   |

| Loop Closure Detector Threshold <sup>1</sup> :                  |          |                   |              |      |

| Programming Accuracy at 10 mA                                   | _        |                   | ±20          | %    |

| Ring Ground Detector Threshold <sup>2</sup> :                   |          |                   |              |      |

| $R_{ICM} = 83 \text{ k}\Omega$                                  | 3        | 6                 | 10           | kΩ   |

| Programming Accuracy                                            | _        | _                 | ±25          | %    |

| Ring Trip Comparator:                                           |          |                   |              |      |

| Input Offset Voltage <sup>3</sup>                               | _        | ±10               | _            | mV   |

| Internal Voltage Source (L8560A/D/E/F)                          | -8.6     | -8.2              | -7.6         | V    |

| Internal Voltage Source (L8560C)                                | -6.1     | <b>−</b> 5.7      | <b>−</b> 5.1 | V    |

| Current at Input RTSP <sup>4</sup>                              | In – 0.5 | ľΝ                | In + 0.5     | μΑ   |

| RCVN, RCVP:                                                     |          |                   |              |      |

| Input Bias Current                                              | _        | -0.2              | -1           | μΑ   |

| Loop Closure Detector Hysteresis                                | _        | 2                 | _            | mΑ   |

| Variation                                                       | _        | 15                | _            | %    |

| THD $^3$ at VPT/PR = 2.2 Vrms, VoH = 12 V, ZT = 200 $\Omega$    | _        | _                 | -35          | dB   |

| VITR Output Impedance                                           | _        | 5                 | _            | Ω    |

| VITR Output Offset Voltage                                      | _        | 20                | _            | mV   |

| Average/dc Current to FB1 and FB2                               | _        | 29                | _            | μΑ   |

| Tested as:                                                      |          |                   |              |      |

| ( FB1 (FB) (-5 V)  +  FB1 (FB) (-63 V)  + 2 FB1 (FB) (-35 V)  + |          |                   |              |      |

| FB2 (FB) (-5 V)  +  FB2 (FB) (-63 V)  + 2 FB2 (FB) (-35 V)  +   |          |                   |              |      |

| FB1 (RB) (-5 V)  +  FB1 (RB) (-63 V)  + 2 FB1 (RB) (-35 V)  +   |          |                   |              |      |

| FB2 (RB) (-5 V)  +  FB2 (RB) (-63 V)  + 2 FB2 (RB) (-35 V) )/16 |          |                   |              |      |

| Accuracy                                                        | _        |                   | ±8           | %    |

<sup>1.</sup> Loop closure threshold is programmed by resistor RLCTH from pin LCTH to pin DCOUT.

2. Ring ground threshold is programmed by resistor RICM2 from pin ICM to VCC.

Table 8. Uncommitted Op Amp Characteristics (44-Pin PLCC Only)

| Parameter                                     | Min | Тур  | Max | Unit      |

|-----------------------------------------------|-----|------|-----|-----------|

| Input Offset Voltage                          | _   | ±5   | _   | mV        |

| Input Offset Current                          | _   | ±10  | _   | nA        |

| Input Bias Current                            | _   | 200  | _   | nA        |

| Differential Input Resistance                 | _   | 1.5  | _   | $M\Omega$ |

| Output Voltage Swing (R <sub>L</sub> = 10 kΩ) | _   | ±3.5 | _   | Vpk       |

| Output Resistance (Avcl = 1)                  | _   | 2.0  | _   | Ω         |

| Small-signal GBW                              | _   | 700  |     | kHz       |

<sup>3.</sup> This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>4.</sup> In is the sourcing current at RTSN. Guaranteed if In is within 5  $\mu A$  to 30  $\mu A$ .

**Table 9. ac Feed Characteristics**

| Parameter                                                                                                                                                                    | Min                   | Тур                     | Max                        | Unit                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|----------------------------|-----------------------|

| ac Termination Impedance <sup>1</sup>                                                                                                                                        | 150                   | _                       | 1300                       | Ω                     |

| Longitudinal Impedance                                                                                                                                                       | _                     | 0                       | _                          | Ω                     |

| Total Harmonic Distortion—200 Hz to 4 kHz <sup>2</sup> : Off-hook On-hook                                                                                                    |                       |                         | 0.3<br>1.0                 | %<br>%                |

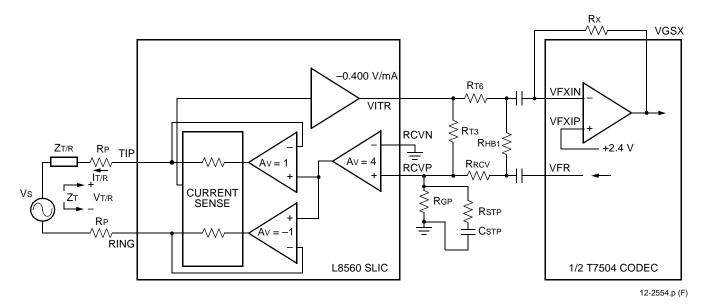

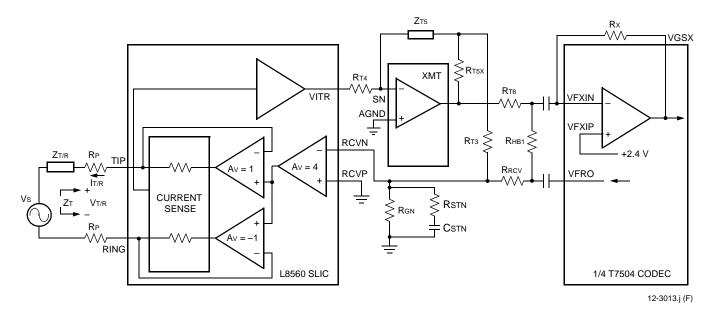

| Transmit Gain, f = 1 kHz (PT/PR to VITR; see Figure 11.)                                                                                                                     | -392                  | -400                    | -408                       | V/A                   |

| Receive + Gain, f = 1 kHz (RCVP to PT/PR) Receive - Gain, f = 1 kHz (RCVN to PT/PR)                                                                                          | 7.76<br>-7.76         | 8.00<br>-8.00           | 8.24<br>-8.24              |                       |

| Group Delay <sup>2</sup> : Transmit, Powerup Receive                                                                                                                         |                       | 1<br>0.5                |                            | μs<br>μs              |

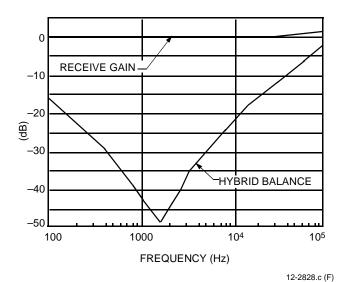

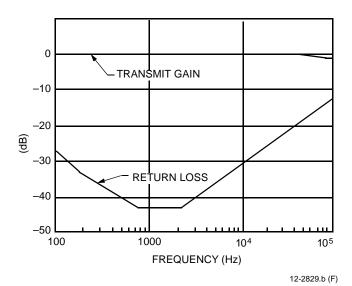

| Gain vs. Frequency (transmit and receive) (600 Ω termination; reference 1 kHz, 1 Vrms) <sup>2</sup> : 200 Hz to 300 Hz 300 Hz to 3.4 kHz 3.4 kHz to 16 kHz 16 kHz to 266 kHz | -1.00<br>-0.3<br>-3.0 | 0.0<br>0.0<br>-0.1<br>— | 0.05<br>0.05<br>0.3<br>2.5 | dB<br>dB<br>dB<br>dB  |

| Gain vs. Level (transmit and receive)(reference 0 dBV) <sup>2</sup> : –55 dB to +3 dB                                                                                        | -0.05                 | 0                       | 0.05                       | dB                    |

| Return Loss <sup>2, 3</sup> :<br>200 Hz to 500 Hz<br>500 Hz to 3400 Hz                                                                                                       |                       | 30<br>36                |                            | dB<br>dB              |

| 2-wire Idle-channel Noise (600 $\Omega$ termination): Psophometric <sup>2</sup> C-message 3 kHz Flat <sup>2</sup>                                                            | _<br>_<br>_           | -87<br>2<br>10          | -77<br>12<br>20            | dBmp<br>dBrnC<br>dBrn |

| 4-wire Idle-channel Noise: Psophometric <sup>2</sup> C-message 3 kHz Flat <sup>2</sup>                                                                                       | _<br>_<br>_           | -82<br>7<br>15          | -77<br>12<br>20            | dBmp<br>dBrnC<br>dBrn |

| Transhybrid Loss <sup>3</sup> : 200 Hz to 500 Hz 500 Hz to 3400 Hz                                                                                                           |                       | 30<br>36                |                            | dB<br>dB              |

<sup>1.</sup> Set by external components. Any complex impedance R1 + R2 || C between 150  $\Omega$  and 1300  $\Omega$  can be synthesized. 2. This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>3.</sup> Return loss and transhybrid loss are functions of device gain accuracies and the external hybrid circuit. Guaranteed performance assumes 1% tolerance external components. Not tested in production.

**Table 10. Logic Inputs and Outputs**

| Parameter                                                                                                                                                 | Symbol     | Min      | Тур  | Max        | Unit   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------|------------|--------|

| Input Voltages: Low Level (permissible range) High Level (permissible range)                                                                              | VIL        | -0.5     | 0.4  | 0.7        | V      |

|                                                                                                                                                           | VIH        | 2.0      | 2.4  | Vcc        | V      |

| Input Currents:  Low Level (Vcc = 5.25 V, Vı = 0.4 V)  High Level (Vcc = 5.25 V, Vı = 2.4 V)                                                              | IIL        | -75      | -115 | -300       | μΑ     |

|                                                                                                                                                           | Іін        | -40      | -60  | -100       | μΑ     |

| Output Voltages (open collector with internal pull-up resistor): Low Level (Vcc = 4.75 V, IoL = 360 $\mu$ A) High Level (Vcc = 4.75 V, IoH = $-20~\mu$ A) | Vol<br>Voh | 0<br>2.4 | 0.2  | 0.4<br>Vcc | V<br>V |

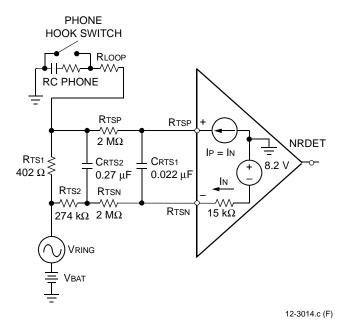

### **Ring Trip Requirements**

- Ringing signal:

- Voltage, minimum 35 Vrms, maximum 100 Vrms.

- Frequency, 17 Hz to 23 Hz.

- Crest factor, 1.4 to 2.

- Ringing trip:

- ≤100 ms (typical), ≤250 ms (V<sub>BAT</sub> = -33 V, loop length = 530 Ω).

- Pretrip:

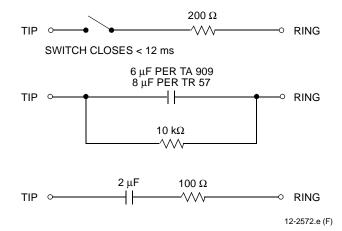

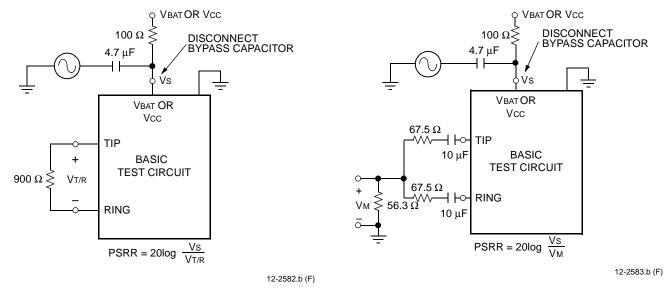

- The circuits in Figure 4 will not cause ringing trip.

Figure 4. Ring Trip Circuits

# **Test Configurations**

Figure 5. Basic Test Circuit

Figure 6. Metallic PSRR

Figure 7. Longitudinal PSRR

# **Test Configurations** (continued)

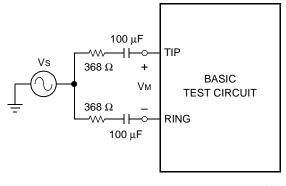

LONGITUDINAL BALANCE =  $20 \log \frac{Vs}{VM}$

12-2584.c (F)

**ILONG** TIP VPT **BASIC** TEST CIRCUIT VPR **ILONG** RING  $Z LONG = \frac{\Delta \ VPT}{\Delta \ ILONG} \ OR \frac{\Delta VPR}{\Delta \ ILONG}$

12-2585.a (F)

Figure 8. Longitudinal Balance

5-6756.a (F)

Vs = 0.5 Vrms 30% AM 1 kHz modulation.

f = 500 kHz—1 MHz.

Device in powerup mode 600  $\Omega$  termination.

Figure 9. RFI Rejection

Figure 10. Longitudinal Impedance

Figure 11. ac Gains

<sup>\*</sup> HP is a registered trademark of Hewlett-Packard Company.

# **Applications**

#### **Characteristic Curves**

Figure 12. L8560 Receive Gain and Hybrid Balance vs. Frequency

Figure 14. L8560 Typical Vcc Power Supply Rejection

Figure 13. L8560 Transmit Gain and Return Loss vs. Frequency

Figure 15. L8560 Typical VBAT Power Supply Rejection

### Characteristic Curves (continued)

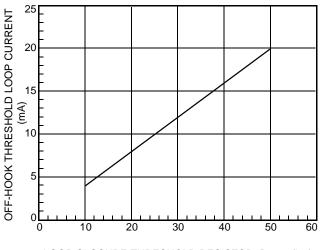

LOOP CLOSURE THRESHOLD RESISTOR, RLCTH ( $k\Omega$ )

12-3015 (F)

Note: VBAT1 = -48 V, ITR =  $1.2 \times 10^{-3} \text{ RLCTH } (\text{k}\Omega)$ .

Figure 16. Loop Closure Program Resistor Selection

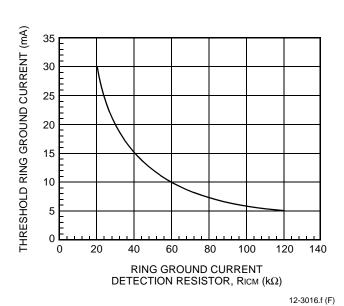

Note: Tip lead is open; VBAT1 = -48 V.

Figure 17. Ring Ground Detection Programming

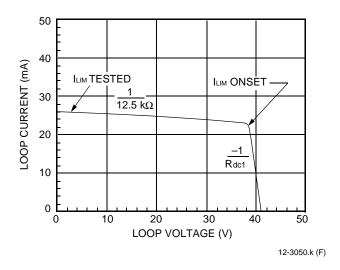

Note: VBAT1 = -48 V; ILIM = 22 mA; Rdc1 = 55  $\Omega$ .

Figure 18. Loop Current vs. Loop Voltage

Note: VBAT1 = -48 V; ILIM = 22 mA; Rdc1 =  $55 \Omega$ .

Figure 19. Loop Current vs. Loop Resistance

#### Characteristic Curves (continued)

Note: VBAT1 = -48 V; ILIM = 22 mA; Rdc1 = 55  $\Omega$ .

12-3032 (1

Figure 20. L8560 Typical SLIC Power Dissipation vs. Loop Resistance

Figure 21. Power Derating

#### dc Applications

#### **Battery Feed**

The dc feed characteristic can be described by:

$$V_{T/R} = \frac{\left(\left|V_{BAT}\right| - V_{OH}\right) \times R_{L}}{R_{L} + 2R_{P} + R_{dc}}$$

$$I_{L} = \frac{\left|V_{BAT}\right| - V_{OH}}{R_{L} + 2R_{P} + R_{dc}}$$

where:

IL = dc loop current.

$V_{T/R} = dc loop voltage.$

|VBAT| = battery voltage magnitude.

Note: The L8560 has a battery switch circuit that allows use of a primary battery, VBAT1, or an auxiliary battery, VBAT2. |VBAT| is the battery, VBAT1 or VBAT2, that is active. See the Battery Switch section for more information.

Voh = overhead voltage. This is the difference between the battery voltage and the open loop tip/ring voltage.

RL = loop resistance, not including protection resistors.

RP = protection resistor value.

Rdc = SLIC internal dc feed resistance.

The design begins by drawing the desired dc template. An example is shown in Figure 22.

Note: VBAT1 = -48 V; ILIM = 22 mA; Rdc1 = 55  $\Omega$ .

Figure 22. Loop Current vs. Loop Voltage

#### dc Applications (continued)

Starting from the on-hook condition and going through to a short circuit, the curve passes through two regions:

Region 1: On-hook and low loop currents. In this region, the slope corresponds to the dc resistance of the SLIC, Rdc1 (default is 55  $\Omega$  typical). The open circuit voltage is the battery voltage less the overhead voltage of the device, VoH (default is 6.7 V typical). These values are suitable for most applications but can be adjusted if needed. For more information, see the sections titled Adjusting dc Feed Resistance or Adjusting Overhead Voltage.

Region 2: Current limit. The dc current is limited to a starting value determined by external resistor RPROG, an internal current source, and the gain from tip/ring to pin DCOUT. Current limit is set by the equation:

IPROG X RPROG = ILIM X BDCOUT

Where:

IPROG = the current from an internal current source

RPROG = the external resistor used to set the current limit

BDCOUT = the transconductance from tip/ring to DCOUT, which is nominally 41.67 V/A

During nonringing modes, the internal current source is set at 75  $\mu A$ , thus:

$IPROG \times RPROG = ILIM \times BDCOUT$

$R_{PROG} = I_{LIM} \times B_{DCOUT}/I_{PROG}$

RPROG (K) =  $ILIM (mA) \times 0.04167 (V/mA)/75e-3 (mA)$

RPROG (K) =  $0.556 \times ILIM (mA)$

Testing data shows that:

RPROG (K) =  $0.616 \times ILIM (mA)$

This equation is a first-order estimation of the loop current at current-limit range.

For more precise loop current at current-limit range, the loop current is also determined by loop length, protection resistance, and battery voltage. It can be shown through calculations as follows:

Current-limit onset (ILonset):

$$I_{Lonset}(mA) = \frac{R_{PROG}(K)}{0.616}$$

Loop resistance where current-limit onsets (RLonset):

RLonset (

$$\Omega$$

) =  $\frac{(|V_{BAT}| - V_{OH})(V)}{|I_{Lonset}(mA)|} \times 1000 - 2R_P - Rdc$

Tip/ring voltage where current-limit onsets (VT/Ronset):

$$V_{T/Ronset} = \frac{(|V_{BAT}| - V_{OH}) \times R_{Lonset}}{R_{Lonset} + 2R_{P} + Rdc}$$

Tip/ring voltage when loop resistance is Rloop (VT/Rloop):

$V_{T/Rloop}(V) = I_{loop}(mA) \times R_{LOOP}(\Omega)/1000$

Loop current is now given by:

lloop (mA) = ILonset (mA) + (VT/Ronset – VT/Rloop) (V)/12.5 (k $\Omega$ )

O

$$Iloop (mA) = \frac{ILonset(mA) + VT/Ronset(V)/12.5(k\Omega)}{1 + Rloop (\Omega)/12500(k\Omega)}$$

Current limit is not sensitive to temperature variation.

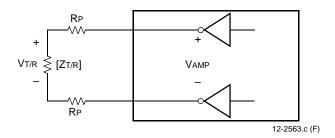

#### **Overhead Voltage**

In order to drive an on-hook ac signal, the SLIC must set up the tip and ring voltage to a value less than the battery voltage. The amount that the open loop voltage is decreased relative to the battery is referred to as the overhead voltage and is expressed as:

$$VOH = |VBAT| - (VPT - VPR)$$

Without this buffer voltage, amplifier saturation will occur and the signal will be clipped. The L8560 is automatically set at the factory to allow undistorted on-hook transmission of a 3.17 dBm signal into a 900  $\Omega$  loop impedance.

The drive amplifiers are capable of 4 Vrms minimum (VAMP). So, the maximum signal the device can guarantee is:

$$V_{T/R} = 4 V \left( \frac{|Z_{T/R}|}{|Z_{T/R}| + 2R_P} \right)$$

For applications where higher signal levels are needed, e.g., periodic pulse metering, the 2-wire port of the SLIC can be programmed with pin DCR (pin DCR is not available in the 32-pin PLCC package). The first step is to determine the amount of overhead voltage needed. The peak voltage at output of tip and ring amplifiers is related to the peak signal voltage by:

$${\stackrel{\Lambda}{V}}_{AMP} = {\stackrel{\Lambda}{V}}_{T/R} \left( 1 + \frac{2RP}{|Z_{T/R}|} \right)$$

#### dc Applications (continued)

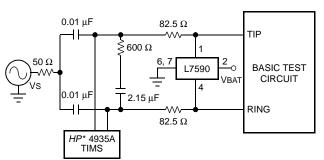

Figure 23. SLIC 2-Wire Output Stage

In addition to the required peak signal level, the SLIC needs about 2 V from each power supply to bias the amplifier circuitry. It can be thought of as an internal saturation voltage. Combining the saturation voltage and the peak signal level, the required overhead can be expressed as:

$$\begin{split} \text{Voh} &= \text{Vsat} + \left(1 + \frac{2R_P}{|Z_{T/R}|}\right)^{\Lambda}_{VT/R} \\ &= \text{Vsat} + \left(1 + \frac{2R_P}{|Z_{T/R}|}\right) \sqrt{\frac{2|Z_{T/R}|}{1000}} \text{ x } 10^{\text{dBm/20}} \end{split}$$

where VsaT is the combined internal saturation voltage between the tip/ring amplifiers and VBAT (4.0 V typ.). RP  $(\Omega)$  is the protection resistor value. ZT/R  $(\Omega)$  is the ac loop impedance.

# **Example 1, On-Hook Transmission of a Meter Pulse:**

Signal level: 2.2 Vrms into 200  $\Omega$  35  $\Omega$  protection resistors

ILOOP = 0 (on-hook transmission of the metering signal)

Voh =

$$4.0 + \left(1 + \frac{2 \times 35}{200}\right) \sqrt{2} (2.2)$$

=  $8.2 \text{ V}$

Accounting for Vsat tolerance of 0.5 V, a nominal overhead of 8.7 V would ensure transmission of an undistorted 2.2 V metering signal.

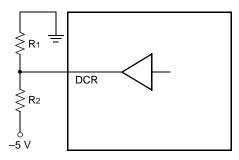

#### **Adjusting Overhead Voltage**

To adjust the open loop 2-wire voltage, pin DCR (44-pin PLCC only) is programmed at the midpoint of a resistive divider from ground to either –5 V or VBAT. In

the case of –5 V, the overhead voltage will be independent of the battery voltage. Figure 24 shows the equivalent input circuit to adjust the overhead.

12-2562.b (F)

Figure 24. Equivalent Circuit for Adjusting the Overhead Voltage

The overhead voltage is programmed by using the following equation:

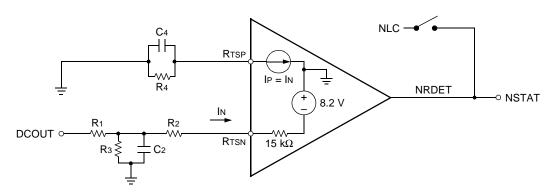

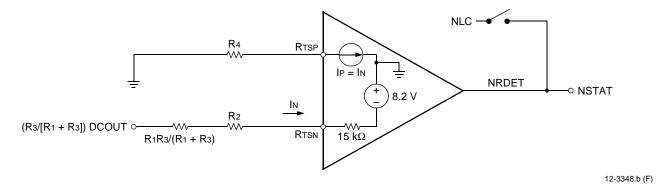

Voh = 7.1 – 18.18 Vdcr